基于DDS的电路板检测仪信号源设计

0 引言

某型导弹测试设备电路板检测仪主要完成该测试设备的电路板的故障检测。该检测系统要求激励信号产生电路体积小,配置灵活,且精度高、转换速度快。基于FPGA的DDS信号发生器较传统信号发生器能够更好地满足检测仪要求。

直接数字频率合成(Direct Digital Synthesize,DDS)是从相位概念出发直接合成所需波形的一种频率合成技术。它是继直接频率合成和间接频率合成之后发展起来的第三代频率合成技术,突破了前两代频率合成法的原理,从“相位”的概念出发进行频率合成,这种方法不仅可以产生不同频率的正弦波、方波、三角波,而且可以控制波形的初始相位,还可以用此方法产生任意波形,目前得到了广泛的应用。

1 DDS的工作原理和基本结构

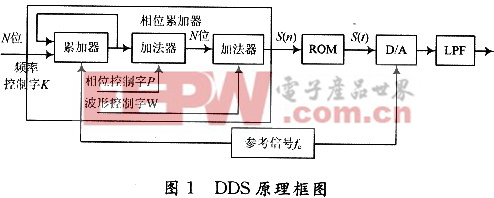

一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器构成。DDS的原理框图如图1所示。

图1中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟,fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P,波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位的幅度码经D/A转换器变成阶梯波,再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形形状取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。

设频率控制字是K,输出频率为f0,参考时钟是fc,相位寄存器为N位,频率分辨率是△f,则有:

通过频率控制字的改变和寄存器位数的增加,可以得到令人满意的频率。

2 基于FPGA的DDS信号发生器的设计

该信号发生器是作为电路板检测仪的激励信号源,产生的信号分别为:频率为16 000±0.8 Hz的正弦波,频率为128 000±6.4 Hz,64 000±3.2 Hz,4 000±O.2 Hz的方波和周期为10μs,占空比为1:4的脉冲信号。下面以正弦波的产生为例说明DDS的实现过程。当f0=16 000 Hz,N=16时,根据式(1),则K=104。

2.1 相位累加器

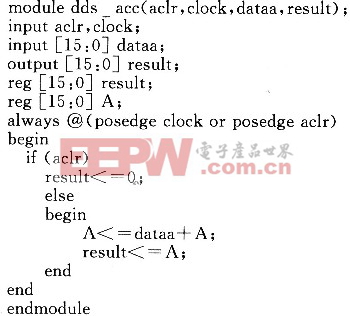

相位累加器主要是根据频率控制字生成ROM查找表的地址,采用硬件描述语言Verilog DHL实现,其源程序为:

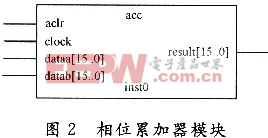

文本输入完毕后,用QuartusⅡ进行编译,然后生成.bsf文件,以便在顶层设计时调用。其生成顶层模块如图2所示。

评论