高速并行RS解码器

1 引言

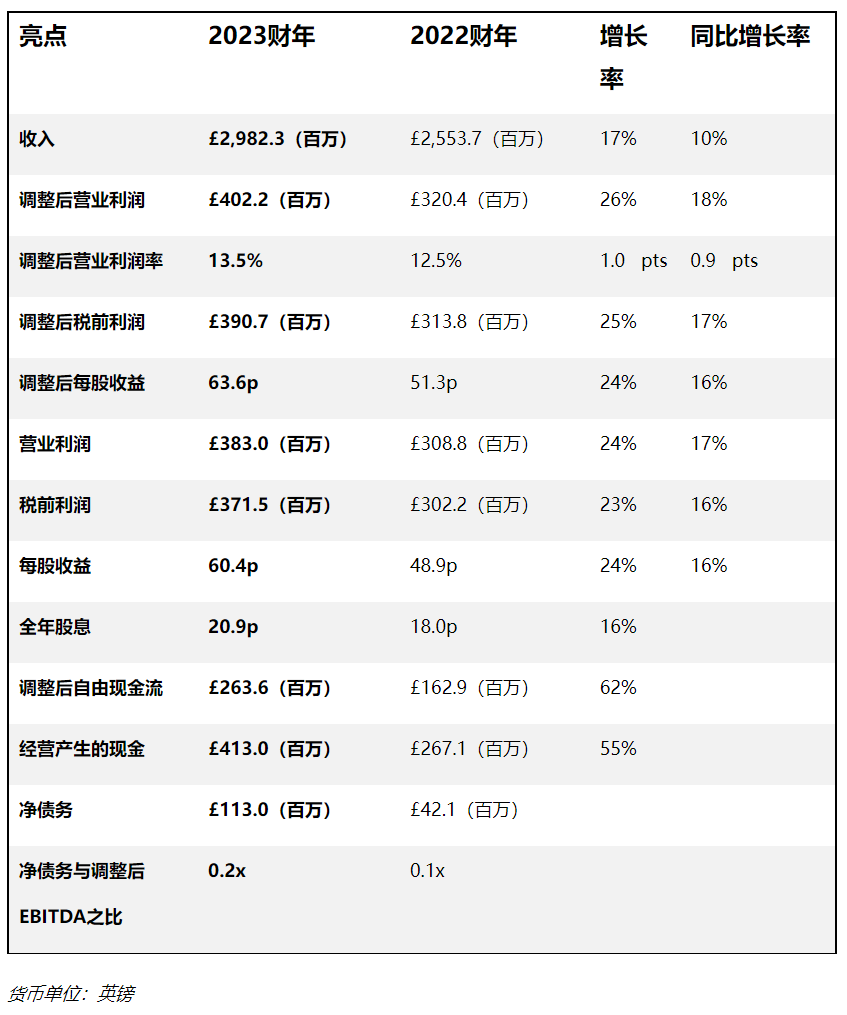

本文引用地址:http://www.amcfsurvey.com/article/151432.htmReed-Solomon(简称RS)码是差错控制领域中一类重要的线性分组码,具有较强的纠正突发错误和随机错误的能力,广泛应用于各种差错控制领域。RS解码器可在FPGA或ASIC上实现IP核。但目前国内编码速度约为400 Mb/s,纠错能力为4 bit,仍存在编码速度低、纠错能力不完善、系统的吞吐率受限等问题。因此提出一种改进的IBM算法.进一步提高RS编码器的编码速度及纠错能力,扩大应用范围。这样RS编解码器能够实现远距离传输信息,太空航天通信的快速存储及全球定位系统需求。

2 RS编解码原理

2.1 编码原理

m=(m0,m1…mk-1)表示GF(28)的k位信息符号序列,该信息矢量多项式:m(x)=m+m1x+…+mk-lxk-1。将左移2t位的信息多项式与生成多项式g(x)相除,得到:p(x)=x2m(x)modg(x),c(x)=x2tm(x)+p(x)。显然,以矢量表示编码后的码字为:C=(p,p,…p,m,m,…m)。编码的码字C中,信息位可以清晰地与校验位区分开。因此,RS编码的实质就是解决以生成多项式g(x)为模的除法问题。

2.2 解码原理

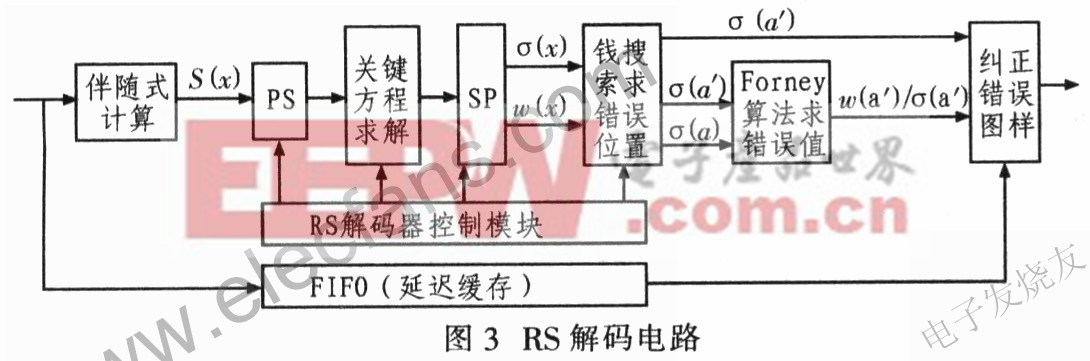

RS解码算法分时域解码算法和频域解码算法。这里主要讨论时域解码算法。时域解码是将码字看成时间轴上的信号序列,利用码的代数结构进行解码。常见的IBM算法解码分为四个步聚:①由接收的码字R(x)计算伴随式S(x);②根据关键方程计算错误值多项式w(a)和错误位置多项式σ(x);③钱搜索找到错误位置,并计算错误值;④纠正错误。图1为RS编解码系统原理图,其中虚线框部分是编码器流程。其余则为解码流程。

3 实现RS(204,188)编解码器

3.1 RS优化的编码方法

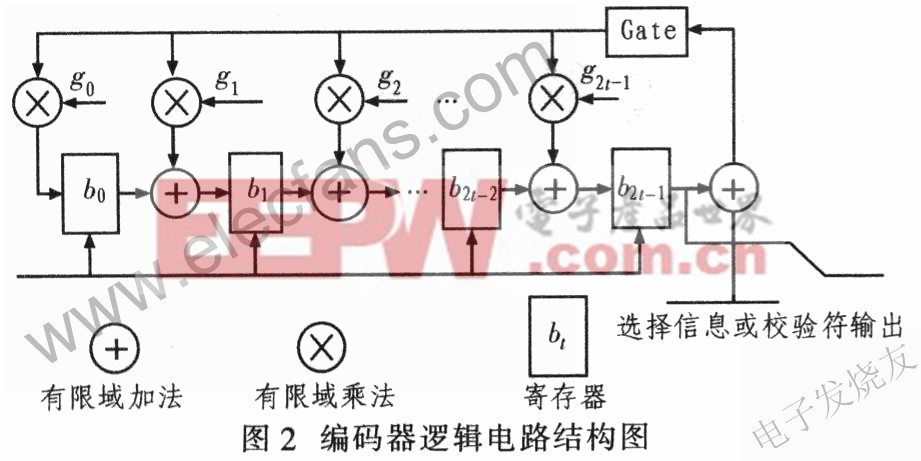

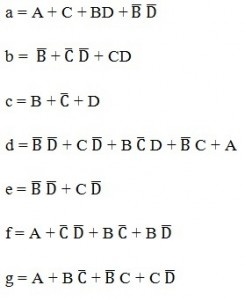

传统的编码器算法实现RS(204,188)编码器,需要16个有限域乘法器和16个有限域加法器。根据RS码型的确定来固定RS码的生成多项式,图2中g0,g1……g15为常数,RS编码器逻辑电路的乘法器则变为常数×变量的形式,利用有限域常数乘法器的特点,对编码器进行两级优化,具体操作如下:①)GF(28)域上的RS(204,188)生成多项式为:g(x)=(x+1)(x+a)(x+a2)…(x+a15),其中a,a2…a15为GF(28)的本原元。生成多项式确定后,计算得到生成多项式的16个系数g0,g1…g15。当有限域乘法器的一个乘数为常数时,乘数运算时只需模2运算所需的异或门而不用与门;②预先计算出现频率较高的并或运算,使用新元素代替矩阵中重复出现的异或计算,这样就实现乘法器结构的第二级优化。

利用上述两种优化RS编码器的乘法器的方法能够实现RS(204,188)编码器,可节省RS(204,188)编码器资源20%。

3.2 解码实现电路

RS(204,188)编码解码器的解码按以下四个步骤实现:①从接收到的码字R(x)计算伴随式S(x);②利用IBM算法计算错误位置多项式σ(x)和错误值多项式w(x);③利用钱搜索算法找出错误位置;④利用Fomey算法计算错误值,与FIFO控制器所存储的接收码字相异或,得到正确的传输码字。图3给出RS(204,188)编解码器的解码电路。

评论