基于OuartusⅡ和GW48EDA开发工具的电子抢答器设计

0 引言

本文引用地址:http://www.amcfsurvey.com/article/151318.htm数字抢答器控制系统在现今许多工厂、学校和电视台等单位所举办的各种知识竞赛中起着不可替代的作用。基于EDA技术设计的电子抢答

器,以其价格便宜、安全可靠、使用方便而受到了人们的普遍欢迎。本文以现场可编程逻辑器件(FPGA)为设计载体,以硬件描述语言VHDL为主要表达方式,以OuartusⅡ开发软件和GW48EDA开发系统为设计工具设计的电子,具有抢答鉴别与锁存功能以及60秒答题限时功能、对抢答犯规的小组进行警告和对各抢答小组进行相应的成绩加减操作等功能。

1 电子抢答器的功能

该电子抢答器实现的功能主要包括四项操作:

(1)第一抢答信号的鉴别和锁存

该电子抢答器共设4个组别,每组控制一个抢答开关,分别为a,b,c,d。在主持人发出抢答指令后,若有参赛者按抢答器按钮,则该组指示灯亮,同时显示器显示出抢答者的组别。同时,电路处于自锁状态,以使其他组的抢答器按钮不起作用。

(2)计时功能

在初始状态时。主持人可以设置答题时间的初时值。在主持人对抢答组别进行确认,并给出倒计时计数开始信号以后,抢答者便可开始回答问题。此时,显示器从初始值开始倒计时,计至0时停止计数,同时扬声器发出超时报警信号。若参赛者在规定的时间内回答完问题,主持人即可给出计时停止信号,以免扬声器鸣叫。

(3)计分功能

在初始状态时,主持人可以给每组设置初始分值。每组抢答完后,由主持人打分,答对一次加1分,答错一次减1分。

(4)犯规设置

对提前抢答者和超时抢答者给予蜂鸣警示,并显示犯规组别。

2 电子抢答器的结构原理

2.1 电子抢答器的整体结构

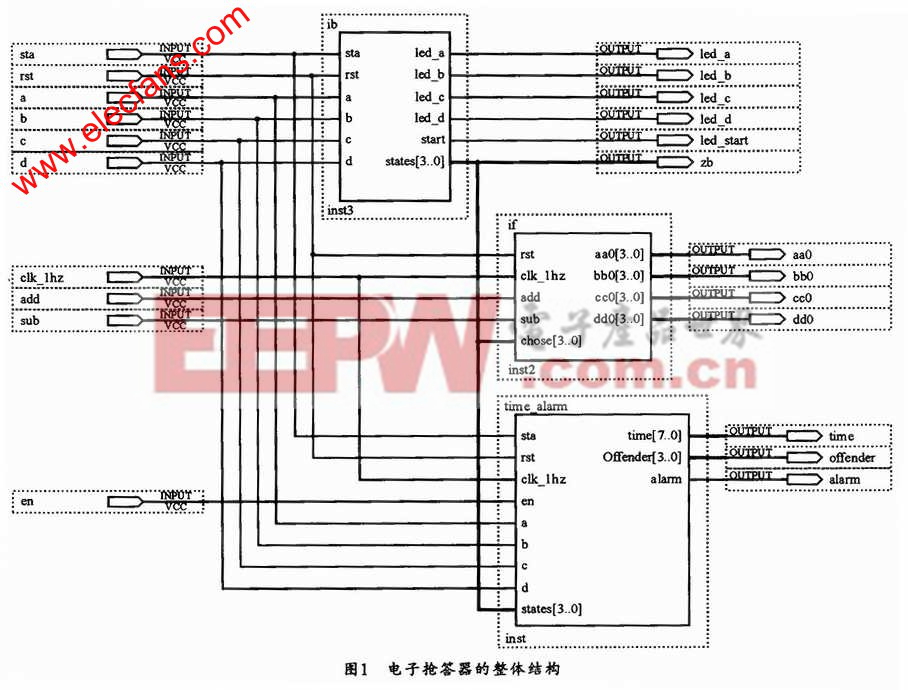

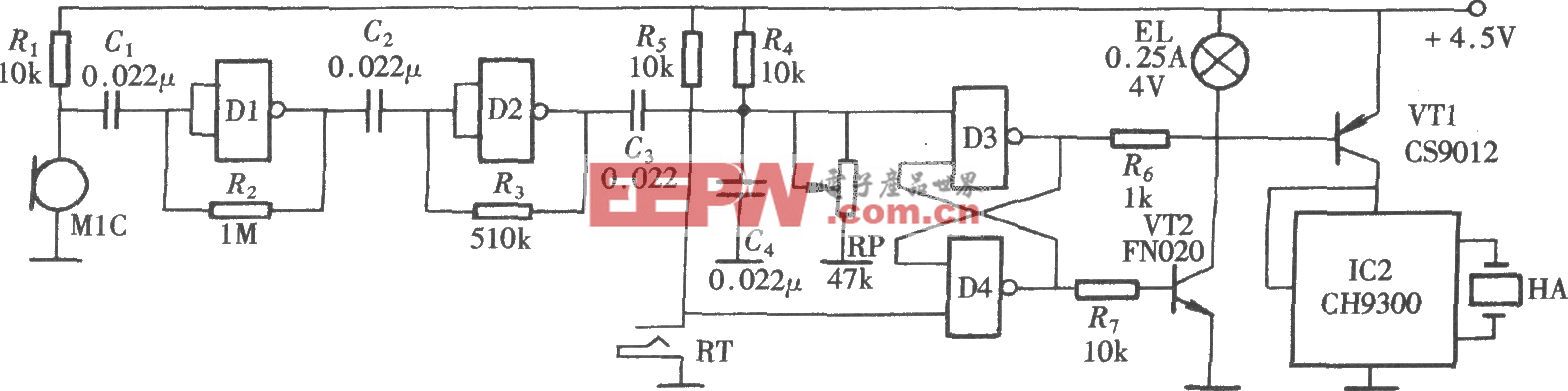

电子抢答器的整体结构如图1所示。它包括鉴别与锁存模块、定时与犯规设置模块以及计分模块。

2.2 鉴别与锁存模块设计

鉴别与锁存模块的主要功能是用于判断a、b、c、d四个组别抢答的先后,记录最先抢答的组别号码,并且不再接受其它输入信号,而对最先抢答的组别锁存,同时显示最先抢答的组别。

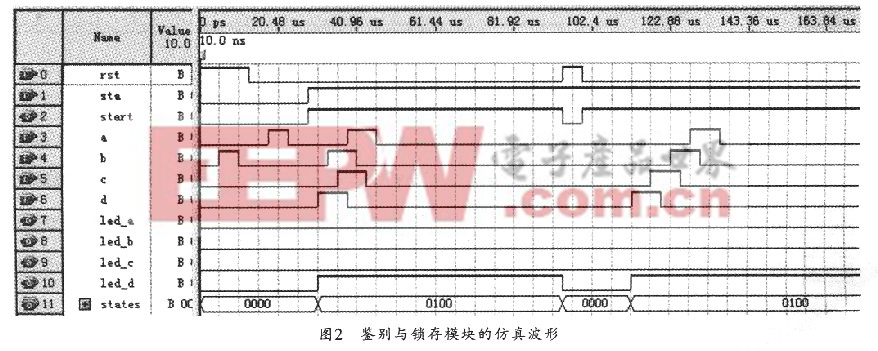

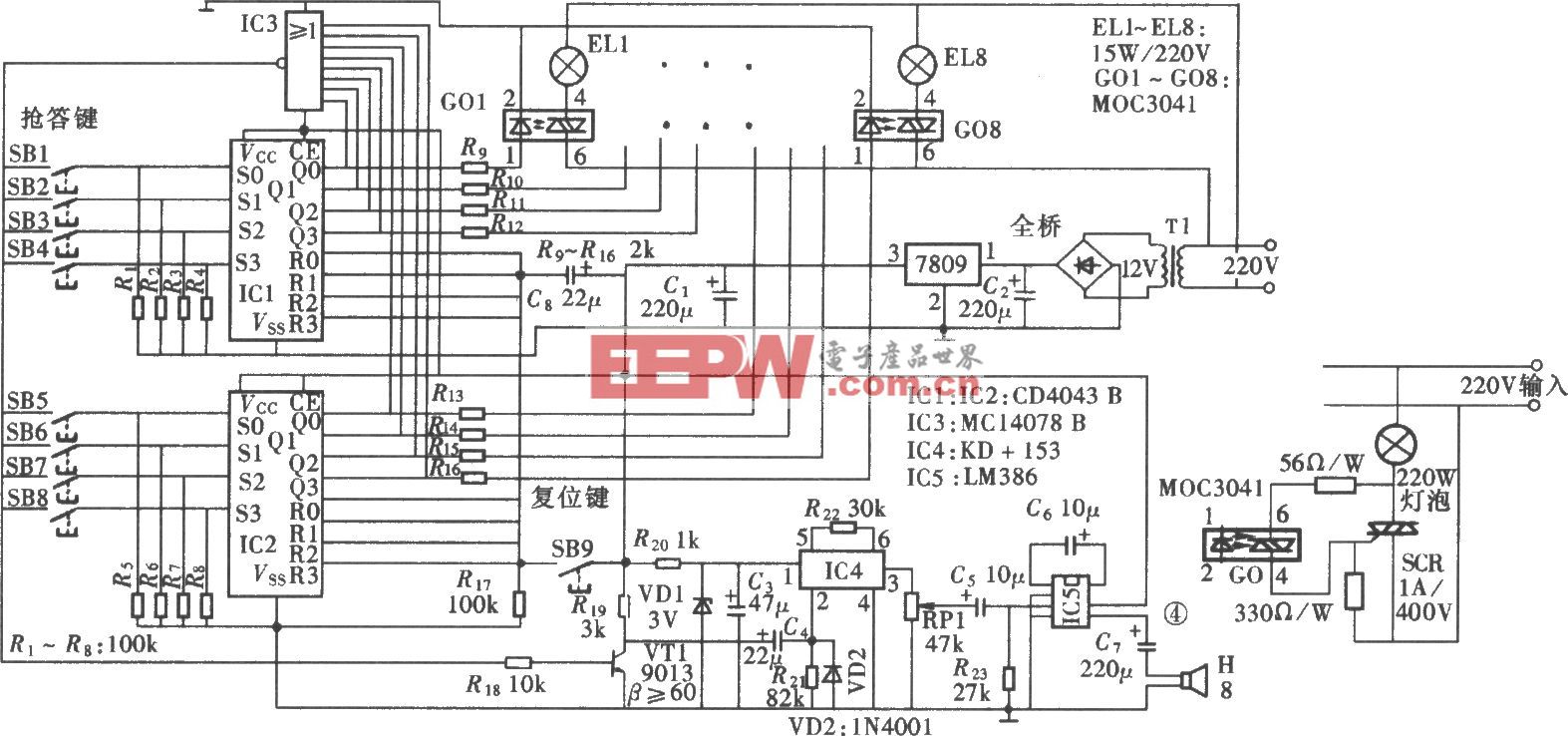

根据以上功能要求,该模块的源程序必须包含四个抢答输入信号。现将其信号分别设为a、b、c、d;抢答时必须要有一个允许开始抢答信号,将其信号设为 sta,该信号输入后,其输出指示灯亮,以便选手知道允许抢答信号已发出,故可设置一个sta的输出指示灯信号为star-t;为了鉴别最先抢答者,可分别设置a、b、c、d组的输出指示灯为led_a、led_b、led_c、led_d,同时设置显示最先抢答组别号码的输出信号为 states[3..0];为了使系统进入重新抢答状态,还需要设置一个系统复位信号,可将其设为rst。其鉴别与锁存模块的仿真波形如图2所示。

通过图2可以看出,当rst=1时,系统处于初始状态,此时所有输入均无效;当rst=O且sta=O时,抢答无效;而当rst=O且sta=1 时,start指示灯亮,d组为最先有效抢答组别,led_d指示灯亮,并显示抢答成功组别d组为“0100”。通过图2的仿真图及分析说明,可见其鉴别与锁存模块的功能设计正确。

评论