基于DSP+ARM架构的协议转换器设计

摘要:介绍基于DSP+ARM架构协议转换器的系统组成及其工作原理,给出了DSP通过EMIF接口与FPGA无缝连接的接口实现,DSP通过HPI接口与ARM高速接口的实现,以及基于ARM的高速以太网接口。简要介绍了基于嵌入式操作系统;uClinux的网络编程,给出了实验结果。

本文引用地址:http://www.amcfsurvey.com/article/151317.htm在测试飞行控制组件时,遥测接收设各离信息处理中心较远,而被测数据量又极大,如果采用传统的专线传输遥测数据,则传输时间需几个小时,无法满足快速处理的要求。因此,需要研制一种协议转换器,用来完成被测数据无损、实时、远距离地与远程上位机进行通信,并能接收上位机的控制指令,实现工作状态的远程交互,而测试人员通过上位机的人机界面就可以完成所有测试。

1、系统组成及工作原理

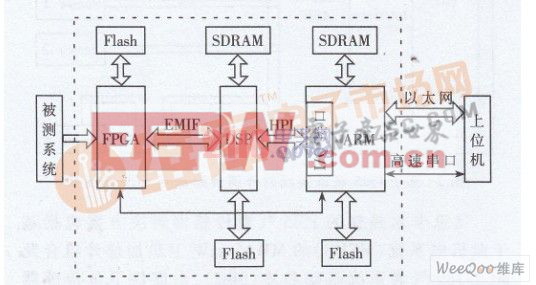

考虑到系统实时性和可靠性的要求,选择以太网口作为协议转换器与远程上位机的数据转发接口、以高速串口作为控制口的通信方式,采用DSP+ARM架构的硬件解决方案。系统框图如图1所示。基本工作原理:FPGA作为数据预处理器,完成并行数据到串行数据的转换等数据预处理任务;DSP读取FPGA处理后的数据并完成数据压缩;ARM作为中央处理控制器,主要从DSP系统中读取已经编码的数据并通过以太网完成与上位机实时通信的任务。上位机按照数据传输协议、产品的数据遥测协议解调出各类物理变量,记录并存储。

图1协议转换器系统框图

测试人员通过上位机完成工作状态的远程设置与查询信息交互的任务。

2、硬件设计

2.1 TMS32OC6416及其外围电路设计

DSP芯片选用TI公司的TMS320C6416。这是TI公司推出的高速定点DSP,它拥有处理能力强大的CPU、高达1 MB的RAM及丰富的外设接口。外设包括为CPU访问外围设备提供无缝接口的灵活的外部存储器接口EMIFA和EMIFB,一个使得DSP很容易通过PCI接口无缝连接到具有PCI功能的外部主CPU上的PCI接口,一个16/32 bit宽的异步并行接口HPI(和Pal共用相同的引脚),一个提供64 bit数据通道访问的增强型EDMA等。TMS320C6416采用3.3 V和1.4 V电源供电,其中I/O采用3.3 V电源供电,内核采用1,4 V电源供电。TMS320C6416有符合IEEE1149,1标准的JTAG标准测试接口及相应的控制器,从而可以通过仿真器把DSP系统与PC机相连,进行在线调试。

2.1.1 DSP与SDRAM、Flash的接口电路

DSP处理器TMS320C6416对外有2个EMIF总线接口,分别是宽64 bit的EMIFA和宽16 bit的EMIFB。EMIFA接口具各与8、16、32、64 bit系统接口的功能,EMIFB接口端口支持8 bit和16 bit系统。EMIFA分成ACE0~ACE3四个存储空间,每个存储空间可以独立配置,无缝连接多种类型的存储器(如SRAM、Flash RAM、DDR RAM)。

为了提高系统运行速度,外扩两片SDRAM芯片作为程序的运行空间、数据及堆栈区。SDRAM芯片选用同步存储器MT48LC2M32B2TG,其容量为2 M×32 bit。TMS-320C6416通过EMIFA接口实现与两片SDRAM芯片的无缝连接。

TMS320C64l6内部没有Flash存储器,为了形成独立的系统,采用外部扩展Flash存储器AM29LV400B存储程序。系统复位时,从Flash中加载程序。TMS320C6416通过EMIFB接口实现与Flash芯片的无缝连接。

2.1.2 DSP与FPGA的接口电路

由于DSP处理器TMS320C6416的采样速度及存储空间受到自身约束限制,所以数据的采集、流向控制和数据预处理等任务由FPGA完成。FPGA芯片选用Xilinx公司低成本现场可编程门阵列Spartan -3E系列中的XC3S500E。XC3S500E芯片集成有⒛个Block RAM,每个RAM块中的18 Kbit的模块存储器是完全同步、真正的双端存储器。用户可独立地从每个端口读出或向每个端口写人(但同一地址不能同时进行读和写)。另外,每个端口都有一个独立的时钟,并且对每个端口的数据宽度都可以独立进行配置。

评论