ISP技术在数字电路实验中的应用

1 ISP技术

在系统编程(In-System-Programming,ISP)技术是美国Lattice半导体公司首先提出来的一种能在产品设计、制造过程中的每个环节具有对其器件、电路或整个数字系统的逻辑和功能随时进行组态或重组能力的最新技术。在可编程逻辑器件(Programming Logic Device,PLD)及其技术中,ISP是一种新的概念、新的标准。传统的编程技术是将PLD器件插在编程器上编程的,ISP技术则可不用编程器,直接在用户自己设计的目标系统中或线路板上对PLD器件编程。常规PLD在使用中通常是先编程后装备,而采用ISP技术的PLD则是先装备后编程,成为产品后还可反复编程。ISP硬件灵活且易于软件修改,便于设计升级。

2 ISP器件的编程软件

ispEXPERT是由Lattice公司提供的一种通用电子设计软件。他支持ABEL-HDL语言、VHDL语言、原理图3种电子设计方式,以及这些设计方式的混合使用。他能对所设计的数字系统进行功能模拟和时序模拟,能对设计进行逻辑优化,并将逻辑映射到器件中去,自动完成预布线,生成编程所需的熔丝图文件,通过下载电缆下载到器件中。

ispEXPERT中的项目导航器引导设计一步步进行,最终生成器件编程所需的JEDEC文件,并下载到ISP器件中。项目导航器是一个很好的设计工具,便于用户跟踪软件的运行流程。

用ispEXPERT对可编程器件进行设计,除了确定设计思想等准备工作外,大部分工作是在计算机上进行的。整个工作流程分为创建新没计项目、选择器件、输入源文件或原理图、编译与优化、逻辑模拟、连接和器件适配等过程。这些过程是在项目导航器引导下进行的。

目前的数字电路课程设计多为用中小规模集成电路和GAL芯片的方法实现。在设计较大规模的数字系统时,由于电路板的限制,过多的集成块使学生花费很多时间都无法调试成功,影响学生的积极性。为此,把ISP器件引入数字电路课程设计,选取了一些有代表性的课题,如多功能电子钟、密码锁、交通灯、数字频率计等,让学生设计实践,取得了很好的效果。

下面举例用ISP对电子钟进行开发设计。

3.1 设计要求

该设计用ispEXPERT软件在ISP1016芯片上实现电子钟的。电子钟具有下述功能:

(1)用实验台上的6个数码管显示时、分、秒。

(2)能使电子钟复位(清零)。

(3)能启动或停止电子钟运行。

(4)在电子钟停止运行状态下,能够修改时、分、秒的值。

(5)具有报时功能,整点时喇叭鸣叫。

3.2 功能分析

电子钟工作时的最高频率是秒针的1 Hz,而实验设备所提供的连续脉冲的最低频率为1 kHz,因而需要一个分频模块,这可通过设计一个模为1 000的计数器设计。

电子钟的秒针是每来一个脉冲计数一次,分针是每过60 s计数一次,时针是每过60 min计数一次,秒针和分针由0计到59又回到0,而时针由0 计到23又回到0。这样需要设计2个模为60的计数器和一个模为24的计数器,例化成秒针模块、分针模块和时针模块。

秒针、分针和时针的计数信号要转换成BCD码后输出,这可以通过在上述各模块内增加一个由二进制码转换为BCD码的编码转换单元实现。

要求能启动或停止电子钟运行,且能在电子钟停止运行状态下修改时、分、秒的值,可增加一个启动/停止控制端实现。如启动/停止控制端接低电平,分频模块的时钟接1 kHz的连续脉冲,其他模块分别接对应输出,电子钟便启动。而当启动/停止控制端接高电平,分频模块的时钟接地,其他模块的时钟分别接3个单脉冲手动输入,电子钟停止运行,手动产生一个单脉冲,与其相连的模块就计数一次,达到了修改时、分、秒的目的,即实现了电子钟更改时间的功能。

3.3 ABEL语言描述

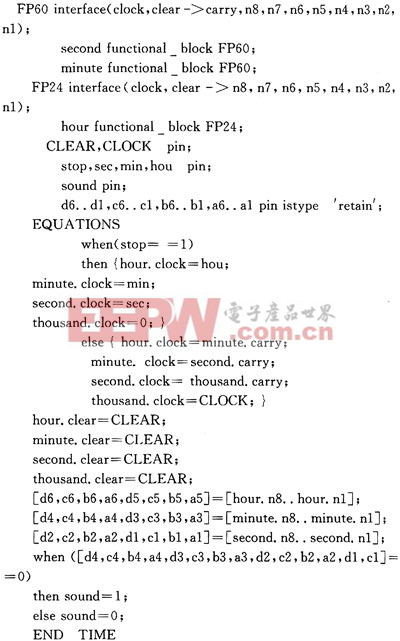

下面用ABEL语言的层次结构实现电子钟的设计可分为顶层模块Clock,3个底层模块FP1000,FP60和FP24。下面介绍顶层模块CLOCK,其中调用了3个底层模块。

4 结 语

从上例可知,用ISP器件可进行各种数字电路实验,代替了古老的面模板实验,而且灵活方便,是一种较理想的数字电路课程设计方法,值得推广应用。

DIY机械键盘相关社区:机械键盘DIY

评论