ARM设计的FPGA可重构配置方法的实现及应用

摘要:文中详述了被动串行配置方式的时序,给出配置流程图及实现的程序代码,并通过实例验证了该方法的优越性及应用前景.通过介绍FPGA的各种配置方式,提出了一种基于ARM处理器的FPGA动态配置方法,充分利用ARM处理器功能强、速度快、应用广的特点,结合FPGA重配置特性,实现了对FPGA的动态配置.

本文引用地址:http://www.amcfsurvey.com/article/151245.htm随着半导体工艺技术的迅猛发展,现场可编程逻辑器件FPGA的集成度迅速提高,已达到百万门量级,与此同时,FPGA中的逻辑资源也日益丰富,使得基于FPGA的片上系统设计成为可能.基于FPGA的片上系统设计因其具有开发周期短,设计成本低,软硬件可编程,系统设计灵活、可裁减、可扩充、可升级等优点正在成为电子系统设计的研究热点,且已经在通讯、工控等领域得到实际应用.

目前FPGA从实现技术上进行分类,可以分为基于查找表(LuT,k—up table)技术,SRAM工艺的FPGA、基于nash技术的FPGA和基于反熔丝(Anti—fuse)技术的FPGA,而使用最多的还是基于SRAM工艺的FPGA,如Altem的Cycl0ne和S tix系列、xilin)【的Spanan和Virtex系列.基于SRAM 的FPGA片内带有存储配置位流的sRAM,上电时,将存储在专用配置芯片中的配置信息加载到FPGA中,从而实现一定的逻辑功能,掉电时片内SRAM中的配置数据遗失,需要下一次加电时重新加载配置.这种片内易失存储器存储配置数据的结构,使得FPGA可以在线动态的对其sRAM中的配置数据进行更新,从而实现电路逻辑功能动态改变.系统可重构主要就是利用基于sRAM的FPGA这种动态重配置特性才得以实现的,下面就以Altem公司Cyclone II系列FPGA分析其配置方式及其可重构应用.

根据FPGA在配置过程中的角色可把cyclone II系列FPGA的配置方式分为三种:FPGA主动串行(As)方式、FPGA被动串行(PS)方式和JATG方式.不同配置模式通过配置模式选择管脚MsEL[1:0]进行选择,其中MsEL[1:0]=o0时选择As模式,MsEL[1:O]=01时选择PS模式,对于某些串行配置器件当MsEL[1:0]=l0时为快速AS模式,配置速度比PS模式快一倍.Cyclone II系列FPGA支持配置数据自解压,将压缩的配置数据存储在配置器件或其它存储器中,配置时传送压缩的位流数据到FPGA中,FPGA可实时的解压缩并对内部sRAM进行编程,配置数据的压缩比例可达35%-5O% ,可有效节省配置存储空间.

在As方式下,由FPGA主动输出控制和同步信号给专用串行配置芯片,配置芯片接收到配置命令后,就开始将配置数据串行的发送至FPGA,完成配置工作.目前常用的专用串行配置芯片为容量为4 Mb的EPCS4和16 Mb的EPcS16等.AS配置模式主要用到四个信号:串行数据输入DcLK、控制信号输入AsDI、片选信号ncs和串行数据输出DATA.

在PS方式下,由系统中其它设备发起配置过程,FPGA在配置过程中只输出应答信号,发起控制配置过程的设备可以是处理器、Altem EPC系列配置芯片、CPLD等功能设备.在下一小节将对PS配置方式做详细的介绍.JTAG调试接口已经作为一个标准接口集成在芯片内,主要用于芯片的测试,cycl0ne II系列FPGA都支持JTAG方式对FPGA进行配置,JrrAG方式具有比其它配置方式都高的优先级.JrI'AG接口定义了四个标准信H号:

● rI℃K测试时钟,各种信号都需要与测试时钟同步;

● TDI测试数据输入,测试数据串行输入,数据在TCK上升沿传送;

● TDO测试数据输出,测试数据串行输出,数据在TCK下降沿传送;

●TMs测试模式选择,决定JTAG电路内部TAP控制器状态机的变化.

2 基于ARM的配置方法及实现

2.1 PS配置原理

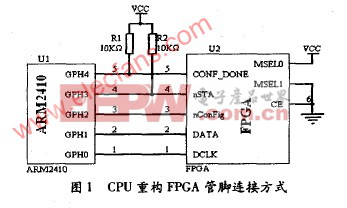

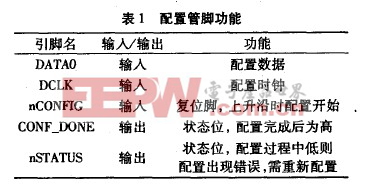

如图l所示,利用s3c2410x作为主控制器采用被动串行方式对EP2c20内部逻辑进行重构.FPGA的PS配置方式是比较常用的一种配置方式,可以有效实现FPGA的在线配置,其基本流程为:在系统中将FPGA被动配置方式配置接口与ARM处理器的IO管脚相连,在处理器端通过软件控制相应管脚的高低电平将数据串行的发送到FPGA中.重构程序运行在ARM处理器中作为实时系统的一个任务,当需要重配FPcA内部逻辑时,调用相应任务,配置完成后,删除当前任务即可,因此,可将预先建立的配置文件库存储到ARM的nash中,由ARM处理器中运行的配置程序来完成动态重构任务。FPGA与Ps配置方式有关的管脚功能如表l所示:

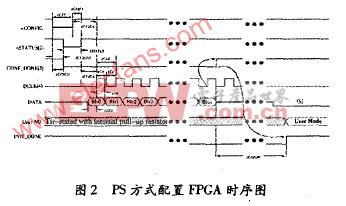

整个配置过程几个关键信号的时序图如图2所示,配置过程可以分为复位、配置和初始化三个阶段:

在复位阶段,微处理器首先在nc0NFIG信号线上产生一个宽度大于8 s的负脉冲,然后开始检测nsTATus信号的状态.FPGA检测到ncONFIG信号的下降沿后会迫使nsTATus和cONF—DONE信号拉低,使FPGA处于复位状态,当ncONFIG变为高电平时,FPGA退出复位状态,释放漏级开路的nSTATUS管脚,nSTATuS在外部需要被l0 K的上拉电阻拉高,nSTATUS管脚变为高电平后,FPGA即进人配置阶段,此时,FPGA已做好了接收配置数据的准备.

FPGA的nsTATuS管脚变高后,延时5 s左右,在DCLK的上升沿FPGA即可从DA L0管脚串行的接收配置数据,配置数据按低位在先高位在后的顺序从数据线上送出.当所有数据都接收完后释放漏级开路的CONFIG— DONE管脚,CONFIG—DONE管脚在外部需要被10 K的上拉电阻拉高,CONFIG—DONE管脚由低到高的跳变表明配置阶段结束,FPGA进入初始化阶段.如果在配置过程中出现错误,则n rATuS管脚将输出低电平,FPGA在内部自动复位,处理器可以通过查询ns1IATuS管脚状态判断在配置过程中是否有错误发生,如果nsTATuS管脚在配置过程中变低则表明有错误发生,如果在软件中设置了错误发生后自动重新开始配置选项则FPcA会延时一段时间后释放nsTATuS,此时nsTATuS被外部上拉电阻拉高,CPu在nsTA—Tus上检测到一个由低到高的跳变后重新开始配置.若软件中未设置“错误发生后自动重新开始配置”选项则需要CPu首先将nCONFIC管脚置低再拉高以开始重新配置.

在初始化阶段,初始化时钟可以是FPGA内部时钟或外部由CLKusR管脚提供的时钟,本例使用了FPGA内部时钟,FPGA将为初始化提供时钟,这样,初始化阶段不再需要外部时钟.初始化阶段完成后INIT—DONE管脚变为高电平,指示FPGA成功进人用户模式,配置过程结束.需要注意的是,若此时CONF—DONE或INIT_DONE未变为高电平,则表明此次配置过程不成功,需要cPu重新进行配置.

评论