QDR SRAM与Spartan3 FPGA的接口设计

为了满足当前系统和处理器的生产量需求,更新的静态存储器应运而生。QDR SRAM就是由Cypress、Renesas、IDT、NEC和Samsung为高性能的网络系统应用而共同开发的一种具有创新体系结构的同步静态存储器。

本文引用地址:http://www.amcfsurvey.com/article/150658.htm 1.1 QDR的先进性

现有的大部分SRAM都是在PC时期针对高效传输PC型单精度输入输出数据而设计的。在大多数的网络应用中,SRAM和记忆控制器之间的连续数据传输是必需的。在这些应用中,存储器的读和写操作之间要进行连续不断的变化。在这种情况下标准的同步管道SRAM等单一的输入/输出装置就不能很好地满足要求。零总线变换SRAM就是一种优化了的SRAM类型。它在读周期与写周期切换时不需要变换周期,从而使得总线利用率达到了100%。而对大多数的网络应用来说,零总线变换SRAM在数据吞吐量方面的提高还远远不够。QDR的出现则进一步改进了SRAM结构。

QDR就是指四倍数据速率SRAM,它是静态存储器的一种,是专为应付带宽需求极大的应用而设计的体系结构。它在一个时钟周期内可以高效地传输4个字节的数据。QDR提供了读和写两个分别独立的接口,从而满足了诸如ATM转换和路由器的性能需求。由于QDR SRAM的结构在数据访问时不需要变换周期且数据吞吐量大幅提高,所以保证了可以对同一地址进行同时访问。

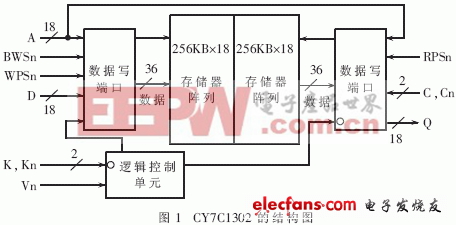

QDR又分为两字突发结构(CY7C1302)和四字突发结构(CY7C1304)两种。这两种结构的不同就在于每次读或写请求的传输字数不同。下面就以CY7C1302为例来详细介绍QDR的工作原理及其与Spartan3系列FPGA的接口设计。CY7C1302是赛普拉斯公司生产的一种QDR SRAM。图1示出了CY7C1302的结构图。图中虽然CY7C1302有了分别独立的读写端口,但是地址总线还是为读写端口共用。地址总线的数据传输采用了DDR的传输方式,即:地址总线的前半个时钟周期提供读操作地址,而后半个时钟周期提供写操作地址。也就是在每个时钟周期可以完成4字的传输量。

1.2 QDR SRAM的输入状态描述

QDR SRAM有四个时钟:K,Kn,C和Cn。K和Kn是用来控制输入数据采样的,C和Cn则是用来控制SRAM数据输出的。所有的数据操作都是在K的上升沿进行的。QDR SRAM有一个简单的控制结构。两个控制信号:读控制信号(RPSn)和写控制信号(WPSn)分别用来控制SRAM的读和写操作的进行。这两种信号在K的上升沿时刻被采样。对QDR来说,地址的输入是读端口和写端口所共用的。对于CY7C1302来说,读操作是在K的上升沿时刻开始进行的,写操作是在Kn的上升沿时刻开始进行的。即地址总线的前半个时钟周期提供读操作的地址,后半个时钟周期提供写操作的地址。其数据线是单向的,在每个循环周期内可以传输两个字的数据。

一个时钟的上升沿可以使QDR SRAM在同一个时钟周期内实现对同一地址的读、写访问。这样QDR就会把写数据传输到读端口以确保把有效的数据输出至数据总线。这样就保证了数据的一致性。

评论