DA算法的FIR滤波器设计

1.引言

在数字信号处理系统中,FIR数字滤波器多采用专用DSP芯片(如TMS320CXX系列),这种基于DSP的处理系统存在很多优点,比如方案灵活、可操作性强、程序易于移植。但这种结构的滤波器多是根据FIR 滤波器的数据移位相乘累加的算法编写相应软件,利用软、硬件相互结合完成滤波器的设计。由于软件运行时,指令都是串行执行的,这严重制约了系统的运行速率,不能满足高传输速率,大数据吞吐量的数字信号的实时性处理要求。而基于DA算法的FPGA滤波器则是一种采用纯硬件的方式实现FIR 滤波器的方式,这种方法突出的优点是运算速度快,特别适合在高速、实时、快变的数字信号处理要求。

2.DA算法的基本思想

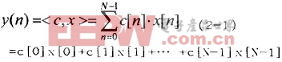

第一个讨论分布式算法(distributed arithmetic,DA)的可以追溯到1973年Cr0i Croisier的一篇论文,并由Peled和Liu来推广。但是直到FPGA出现以后,才在FPG计算乘积和中被广泛地应用。在FPGA 芯片设计中,分布式算法(distributed arithmetic,DA)是一种很重要的技术。它在乘积和的计算中已被广泛应用,为了理解DA算法设计原理,我们考虑有一个线性时不变网络的输出可以用下式表示:

假设系数c[n]是已知常数,x[n]是变量,在有符号DA系统中假设变量x[n]的表达式如下:![]()

其中xb[n]表示 x[n]的第b位,即x[n]是x第n个样点。所以,内积y 可以表示为:![]()

我们重新分别求和次序(这就是分布式算法的由来),结果是:

y=(c[0]xB-1[0]+c[1]+……+c[N-1]xB-1[N-1])2B-1+(c[0]xB-2[0]+c[1]+……+c[N-1]xB-2[N-1])2B-2 (2-4)

.

.

.

+(c[0]x0[0]+c[1]x0[1]+c[N-1]x0[N-1])20

用更紧凑的形式表示为:![]()

从(2—4)式可以发现,分布式算法是一种以实现乘加运算为目的的运算方法。它与传统算法实现乘加运算的不同在于执行部分积运算的先后顺序不同。分布式算法在实现乘加功能时,是通过将各输入数据的每一对应位产生的部分积预先进行相加形成相应的部分积,然后再对各个部分积累加而得到最终的结果,而传统算法是等到所有乘积已经产生之后再来相加完成乘加运算的。与传统串行算法相比,分布式算法可极大地减少硬件电路的规模,提高电路的执行速度。

3.基于DA算法的FIR数字滤波器的硬件实现

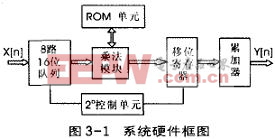

由上面分析可以知道,对于任何一个线性时不变网络总可以将它转换成式(2-5)那样的形式,FIR滤波器是一个很典型的线性时不变网络,它的表达式是:![]()

我们可以将它转化成下面这样的形式:![]()

在本系统中,采用的是8 位输入,所以B = 8 则:![]()

线性相位FIR滤波器满足系数对称条件,本系统设计的系统为16阶,那么它的系数关于h[7]偶对称,即有:

h[n]= h[16-1-n]= h[15-n] (3-4)

由式(3-3)和(3-4)可得到实现系统硬件框图如图3-1:

4.系统的VHDL描述

4.1顶层模块设计

Library ieee;

Use ieee.std_logic_1164.a11;

Use ieee.std_logic_unsigned.all;

Entity FIR is

Port (x: in std_logic_vector(7 downto 0);

clk : in std_logic;

y : out std_logic_vector(7 downto 0));

end FIR;

architecture behave of FIR is

component lpfir

port (

in : in std_logic_vector(7 downto 0);

clk : in std_logic;

out : out std_logic_vector(7 downto 0));

end component ;

begin

process(clk)

begin

u1:lpfir port map (x,clk,y);

end process;

end behave;

4.2 LUT查询表ROM的建立

用MIF文件格式编辑的ROM初始化值

WIDTH = 16

DEPTH = 16

ADDRESS_RADIX = HEX ;

评论