基于FPGA和DSP的高压变频器中性点偏移技术的算法实现

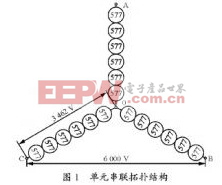

目前国内生产的高压变频器大多采用功率单元串联叠加多电平,VVVF控制方式。其拓扑结构如图1 所示。A、B、C三相各6 个功率单元,每个功率单元输出电压为577 V,相电压UAO=UBO=UCO=3 462 V,线电压UAB=UBC=UCA=6 000 V。如果出现任意1 个功率单元故障旁通时,势必造成系统不平衡,从而导致系统停机。经过公司研发人员的理论推导及技术分析,提出了“中性点偏移”的方法。

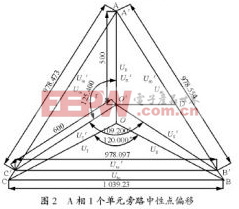

如图2(此图按照等比例1颐5.77所绘)所示,如果A 相有一个功率单元故障旁通掉,中性点由O偏移到O忆(虚拟中性点),经过运算,线电压由原来的1 039.23 V(1 039.23伊5.77=5 996 V)变为978.5 V(978.5伊5.77=5 646),相角度由120毅变为125.4毅和109.2毅。虽然相电压不相等,但是输出的线电压保持相等。这样就保证了电机的三相电流平衡。同理如果出现2 个或3 个单元旁通时,经过复杂运算,也可实现中性点偏移,从而保证输出的线电压相等。

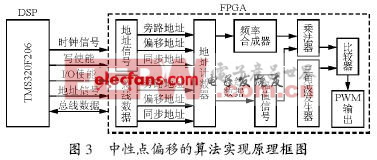

中性点偏移的算法实现,主要是通过现场可编程门阵列(FPGA)和数字信号处理器(DSP)来实现的。DSP 主要采集功率单元的故障信息并进行处理后,发出旁通信号、地址和数据信号给FPGA。

FPGA收到这些数据后,做相应处理。中性点偏移的算法实现原理框图如图3所示。其中,DSP采用TI 公司的TMS320F206,FPGA 采用Altera 公司的EP1C6Q240C8。

2.1 芯片简介

TMS320F206 是TI 公司推出的一种DSP 芯片,它是基于TMS320C5x 之上的高速定点数字处理芯片,具有改进的哈佛结构(程序总线和数据总线分离)、高性能CPU及高效的指令集等特点。其主要特性有:CPU具有32 位CALU、32 位累加器、16伊16 位并行乘法器、3 个移位寄存器、8 个16 位辅助寄存器。存储器具有224 kB 可寻址存储空间、544 B片内DRAM、4 kB 片内SRAM 或32 kB片内快闪存储器。指令速度可达25 ns单指令周期。外围电路有软件可编程定时器、软件可编程等待状态发生器、片内锁相环时钟发生器、同步和异步系列串口等。

EP1C6Q240C8是Altera 公司推出的主流低成本FPGA-Cyclone系列。Cyclone器件采用0.13 滋m的工艺制造,其内部有2 个锁相环(PLL)、20 个M4K RAM块、具有5 980个LE 的逻辑容量、最大用户I/O 为185、支持高速LVDS 接口,性能可达到311 Mb/s。

2.2 DSP数据处理

当故障信号(包括IGBT过流,直流过压,无PWM信号等)上传到DSP 中时,DSP对故障位进行判断,封锁相应故障功率单元的PWM 信号,然后执行旁通程序,对每个功率单元按顺序进行扫描,对有故障的功率单元进行记忆,然后发出旁通命令及对应的旁通地址和相应数据。

2.3 地址信号编码和总线数据处理

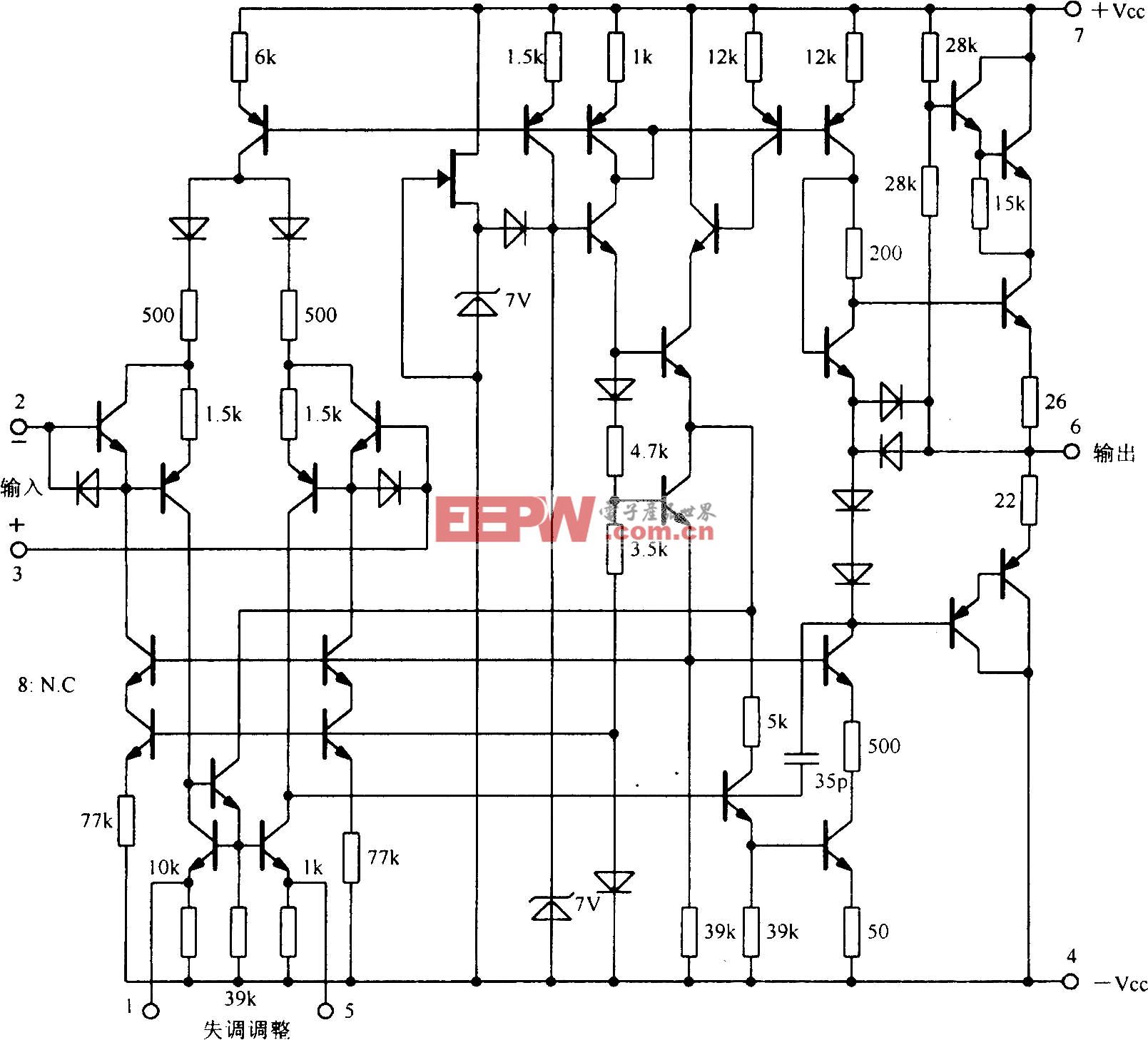

地址信号分为旁通地址、同步地址、偏移地址,均通过ab[7..0]实现。旁通时A、B、C 三相分别对应一个地址。通过此地址DSP 向FPGA 发送旁通命令、同步数据及偏移数据。地址信号编码如图4 所示。

总线数据包括旁通命令位、同步数据量、偏移数据量,通过数据总线gcm_data[15..0]来接收,A、B、C 三相分别对应一个地址。在相应地址选通后,DSP 向FPGA 写数据,由FPGA 来保存这些数据,在数据用完后进行清零。如图4 所示,旁通输出数据为gcm_a_pt_ [15..0]、gcm_b_pt_[15..0]、gcm_c_pt_[15..0],同步和偏移输出数据信号为a_q[15..0]、b_q[15..0]、c_q[15..0]。

在FPGA 中用于查表的地址数据主要用于正弦波查表,改变此地址可生成不同频率的正弦波形。如图4 所示的ab[7..0]有效时,改变gcm_data[15..0] 的值可以产生不同的地址信号a_q[15..0]、b_q[15..0]、c_q[15..0],此三个地址信号用于正弦波查表的地址输入值。

2.4 频率合成器及乘法器的实现

在FPGA 中利用Altera 的quartusII 软件的图形化解决方案,应用Verilog HDL 语言编写子程序,如图5 所示,gcm_lpm_rom 为频率合成器程序图形。频率合成器包括一个11 位最高有效位(MSB)的地址表address [10..0],连接一个SINROM的查阅表(LUT)上,从而产生所需要的输出数据q[7..0]。利用ModelSim软件进行仿真,当地址有效后,输出相应的波形数据,波形如图6 所示。

评论