PLD和数据通路来释放微控制器中CPU资源

本文介绍了一种采用PLD和数据通路(datapath)来解放微控制器系统中CPU任务的方案。在大多数微控制器结构中,智能的CPU身边总会环绕着一系列不可编程的外设。外设的功能有限,通常它们只负责数据形式的转换。例如,I2C外设只是实现串行和并行数据格式之间的转换,而ADC则实现模拟到数字信号的转换。CPU因此不得不完成所有的数据处理工作,实际上它还能做些更有用的事情。此外,管理外设将会导致CPU固件异常复杂,并可能需要一个快速高效的CPU在实时的时序限制下执行这些固件。这又会导致更多的潜在程序漏洞,从而需要使用更复杂和昂贵的调试设备等。

本文引用地址:http://www.amcfsurvey.com/article/150055.htm但是如果外设具备足够的复杂度、灵活度与智能,是否能有效地减轻CPU的许多任务呢?本文将展示如何把智能、灵活、低成本、可定制的数字外围设备设计到微控制器并配置,以帮助实现稳定的分布式系统设计。

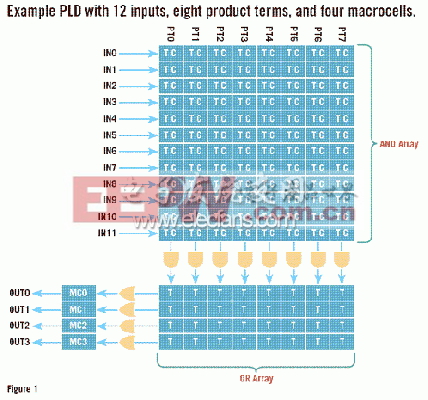

通常有两种方法构建一个智能的可配置外设。首先是使用PLD。如图1所示,PLD有一个驱动若干宏单元的积和(sum of products)逻辑门阵列。“T”和“C”符号表示每一个乘积项都能产生一个真值或补数(反向)输出,这样无论是正、负逻辑都可以支持。

图1:一个PLD实例(包括12个输出项、8个乘积项、4个宏单元)。

图1显示了一个简单的PLD例子。PLD可以有成百上千的宏单元,每个宏单元最高由16个乘积项驱动。乘积项里的与门和或门可以互联形成高度灵活的定制逻辑功能。宏单元是典型的时钟架构,它们的输出可以反馈到乘积项阵列,因此允许创建状态机。

大规模PLD可以用来形成复杂的逻辑功能,甚至是完全的CPU,因此PLD当然可以用来实现智能数字外设。然而,很多门可能只是实现诸如计数器或加法器等简单的逻辑功能,但对于更复杂功能的实现,基于PLD的方案就会变得很贵。从某种程度上说,使用真正的CPU会更合理。

CPU的一个非常简单的形式是基于算术逻辑单元(ALU)的数据通路,也称为纳米处理器(nano-processor)。数据通路只是实现几个常用函数,但会比使用PLD实现的效率更高。图2:显示了一个基于ALU的简单的数据通路。典型的ALU可以进行各种操作,通常是8位操作:向上计数(递增)、向下计数(递减)、加、减、逻辑与、逻辑或、逻辑异或,左位移、右位移。这里有两个8位累加器,它们能够为ALU输出充当输入数据寄存器或存储器。一个输入时钟信号沿产生一次操作。函数选择寄存器用来控制:

图2:基于ALU的数据通路。

* 产生什么操作。

* 该操作的源寄存器。

* 输出的目的寄存器。

评论