基于FPGA的μC/OS-II任务管理硬件设计

实时操作系统RTOS(Real Time Operating System)由于具有调度的实时性、响应时间的可确定性、系统高度的可靠性等特点,被越来越多地应用在嵌入式系统中,如:航空航天、工业控制、汽车电子和核电站建设等众多领域。

本文引用地址:http://www.amcfsurvey.com/article/149646.htm传统上,RTOS内核是加在应用程序中的软件,它不仅增加了ROM(代码空间)和RAM(数据空间)的开销,而且增加了应用程序的额外负荷,即使在设计较好的应用系统中内核仍占用2%~5%的CPU负荷[1]。在实时性较强的场合,若无法得到及时的响应,将会引起严重后果。因此,降低RTOS内核的系统开销及提高其实时性非常重要。

对于降低RTOS占用应用程序处理器开销的研究,大多数集中在改进调度算法[2]和提高处理器的处理能力[3],但是依靠改进调度算法已不能使其实时性有更大的提高,通过提高处理器速度也达不到理想的效果。随着EDA技术的发展及硬件芯片造价的降低,“软件硬件化”的趋势正在成为一个研究的新热点。采用硬件芯片实现RTOS的功能模块极大地发挥了系统处理的并行特性,使硬件RTOS的处理速度达到了传统软件RTOS的6~50倍[4]。然而,RTOS的硬件化非常复杂、繁琐,大多由软件实现的数据结构不适合硬件的并行实现,需要重新修改、设计。

本文就具体的实时操作系统μC/OS-II的任务管理进行了硬件设计,实现了任务管理模块系统调用的硬件电路和基于组合电路的硬件任务调度器。

1 硬件RTOS总体设计

硬件RTOS由软件和硬件两部分组成,如图1所示。软件部分负责应用程序与硬件RTOS的交互,主要实现2点功能:向应用程序提供访问硬件函数的接口;向硬件逻辑提供返回处理结果的中断处理函数和任务切换的中断处理函数。硬件部分将以往由底层软件函数完成的工作,采用硬件函数完成。

硬件RTOS仍然是以系统调用的形式为应用程序服务,所不同的是由调用硬件函数替代了以往的软件函数。软件函数和硬件函数的区别[5]在于:它们被处理时所在的器件不同,软件函数编译成一条条指令在处理器上执行,硬件函数把参数通过数据总线发送到了指定硬件单元电路的寄存器中,再由硬件逻辑电路进行相应的处理。硬件电路与处理器可以并行工作,节省的处理器时间用于执行别的任务,提高了系统的可调度性。

图1中,硬件部分由输入输出寄存器、中断控制器、控制器和RTOS主要功能模块等组成。

(1)输入输出寄存器。输入寄存器接收由接口函数传递的功能代码和参数,输出寄存器将执行结果返回给接口函数。

(2)中断控制器。接收外部事件中断,中断控制器使用FPGA的I/O(输入/输出)管脚,每个管脚对应一个外部中断,一个或者多个外部中断对应一个中断处理任务[6]。当外部中断到来时,相应的事件标志位被置位,中断任务被置为就绪态。

(3)控制器。从事件控制块和信号量控制块获知任务的状态,结合系统调用的功能代码和参数信息,确定将要执行的操作并发出控制信号。每个硬件单元都通过CPU发出的控制信号进行工作。

RTOS主要功能模块包括:事件标志组管理、信号量管理、任务管理及时钟管理。

(1)事件标志组管理。事件标志组是一个数据结构,采用FPGA的片内寄存器实现,每个事件占1 bit。任务或中断服务可以将某一位置位或复位。当任务所需要的事件发生时,则将相应的事件位置位;当任务所等待的事件都发生时,则应向控制器提出改变任务状态的相应申请,同时将任务的ID号送给任务管理模块。

(2)信号量管理。信号量由2部分组成:16 bit的无符号整型的计数值(0~65535);等待该信号量的任务组成的等待任务表。采用可预置的双向计数器(up/down)实现计数值部分,采用FPGA片内的寄存器实现该信号量的等待任务表。寄存器的位数对应系统中的任务数,每个任务占1 bit,且初始值为0(表示没有任务等待该信号量)。等待该信号量的任务将寄存器的相应位置1,释放该信号量的任务唤醒优先级较高的等待任务,将寄存器的相应位置0。每发生一次置位或复位操作,也必须向控制器提出改变任务状态的相应申请,同时将相应任务的ID号送给任务管理模块。

(3)任务管理。负责各种任务状态的切换和任务调度。任务管理模块接收从输入寄存器、事件标志组管理模块或信号量管理模块传递来的任务ID号,在控制器的相应控制信号作用下,执行任务状态的切换。调度器以任务的状态为敏感信号,当任务的状态发生改变时,触发调度器执行一次任务调度,找出当前优先级最高的就绪态任务。若其优先级高于当前正在运行的任务的优先级,则向CPU发出硬件中断处理信号。

(4)定时器管理。主要实现任务的延时,当设置的延时时间到且任务没有等待别的资源时,将任务的状态置为就绪。

由图1可知,硬件RTOS的工作过程如下:

(1)在应用程序中调用系统服务。

(2)系统调用的接口函数将功能代码和参数传给硬件部分的输入寄存器。

(3)硬件部分执行系统调用。

(4)在硬件逻辑执行系统调用的过程中,可以接收外部事件的异步请求,因此,硬件部分执行系统调用过程中可能转向以下不同的处理过程:

①若外部事件请求使中断任务就绪,则向处理器发出要求任务切换的硬件中断请求。

②若系统调用使高优先级的任务就绪,则硬件部分向处理器发出要求任务切换的硬件中断请求。

③硬件部分完成系统调用功能,则采用中断形式通知处理器并回送处理结果。

(5)中断处理函数完成任务切换。

(6)处理器执行新任务。

2 μC/OS-II任务管理硬件设计

任务管理是RTOS的核心,本文首先对μC/OS-II任务管理模块进行了硬件设计,其他的模块可以依托任务管理展开。μC/OS-II任务管理主要包括建立任务、删除任务、挂起任务、恢复任务、查询任务和任务调度等。其中建立任务、删除任务、挂起任务、恢复任务和查询任务是通过系统调用形式交给用户调用的;而任务调度是交给系统函数调用的,用户不能直接调用它。因此,本文将任务管理分成系统调用函数的硬件实现和任务调度器硬件实现2部分。

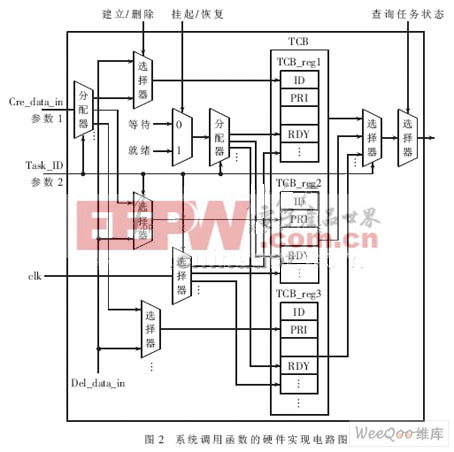

2.1 任务管理系统调用函数的硬件设计

μC/OS-II的任务由3部分组成:即任务程序代码、任务堆栈、任务控制块TCB(Task Control Block)。TCB把任务代码和任务堆栈进行关联而使三者成为一个整体。

任务管理系统调用的硬件实现电路如图2所示。参数1是建立任务时,写入TCB的任务代码段地址、任务优先级、任务的参数指针和分配给任务的堆栈栈顶指针等任务运行和管理的信息;参数2是分配给任务的ID号。每个任务依据任务的ID号对应一个TCB。

在图2中,任务管理系统调用的硬件实现电路主要由分配器、选择器和TCB寄存器组成。

(1)分配器。建立任务和删除任务时,分配器根据任务的ID号选择建立任务的信息送到对应的输出通道上,分配器的输出端与多路选择器的一路输入端直连,即参数1被送到了选择器的输入端,作为一路输入。挂起任务和恢复任务时,分配器根据任务的ID号,将任务的状态送到对应TCB的状态寄存器中。

(2)选择器。选择器的输入端分别是建立任务时要送给 TCB的数据(参数1)和删除任务时要送给TCB的数据(系统初始值),数据输出端与一个TCB块直连。建立信号有效时,选择参数1写入TCB,建立任务完成;否则,写入系统的初始值覆盖TCB信息,即任务被删除。挂起和恢复任务只需根据任务的ID号找到相应的TCB并修改其状态寄存器的值。二值选择器的输入端是0和1,可以分别表示任务的等待和就绪状态。

(3)TCB寄存器。在软件实现的RTOS中,空闲TCB块和已占用的TCB块分别以空闲任务链表和任务链表的形式常驻内存。但是基于链表的软件算法并不适合直接采用硬件高效实现,因为只有读取链表的前一个表项的内容后,才能获得后续表项的地址,限制了硬件并行的开发。因此,本文将TCB的数据结构全部采用片内的寄存器资源实现,从而节省了链表的查找时间,提高了系统调用的执行效率。

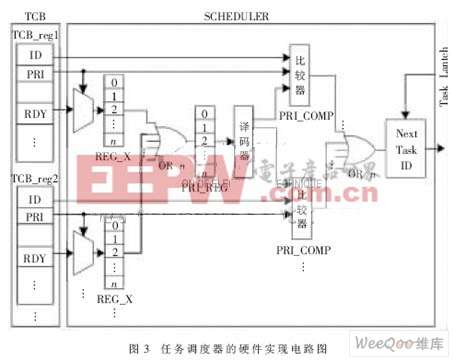

2.2 任务调度器的硬件设计

μC/OS-II进行任务调度的思想是,每时每刻总是让优先级最高的就绪任务处于运行状态。为了实现高效的调度算法,采用组合电路实现硬件调度器,如图3所示。以优先级为选择条件,将TCB中的状态寄存器直接与调度器相连接。这样,只要任务的优先级或任务的状态有一个发生改变,就会立刻引发一次任务的的重新调度。

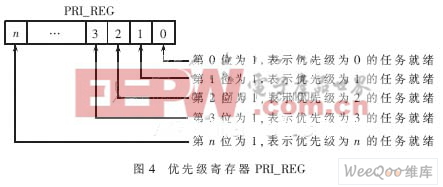

图3中,数据分配器与TCB寄存器中的状态寄存器RDY输出端直连,使用优先级PRI作为选择条件,将RDY的就绪态(RDY=‘1’)分配到不同的输出通道上。寄存器REG_X接收数据分配器输出通道的输出值并按位存储。将所有的REG_X寄存器按位进行或运算,结果送寄存器PRI_REG。如图4所示,优先级寄存器PRI_REG的位数对应系统中任务的个数,寄存器PRI_REG某位为1就表示相应优先级的任务处于就绪态,且低位的优先级依次高于高位的优先级。译码器从寄存器读取PRI_REG的值进行译码,送出处于就绪态且优先级最高的任务。比较器PRI_COMP以任务的ID号为索引,任务的优先级PRI为比较内容。将每个任务的优先级与译码找到的就绪态的最高优先级相比较,若相同,则输出任务的ID号,否则输出0。最后将所有比较器PRI_COMP的输出做或运算,即得到处于就绪态的优先级最高任务的ID号。

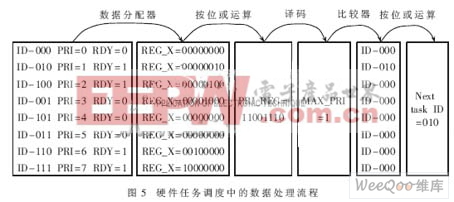

假设在某一时刻,系统中优先级PRI为1、2、3、6和7的任务处于就绪态,对应任务的ID号分别是010、100、001、110和111,则调度器中的数据处理流程如图5所示。

2.3 仿真及实验结果

整个设计采用VHDL硬件语言描述。为了验证该硬件实现的正确性和高效性,使用 ISE 8.2软件进行时序仿真验证。任务管理硬件实现的功能仿真如图6所示。

(1)建立任务。依次建立3个任务,优先级与ID号相同分别为7、1和6。若系统中只有优先级为7的任务处于就绪态,则Next_task_id为7;当建立了优先级为1的任务时,高优先级任务剥夺低优先级任务的CPU使用权,Next_task_id为1,直到有更高优先级的任务到来,或任务自身删除,优先级为1的任务将一直执行。

(2)查询任务。处理器通过查询任务这个系统调用获得任务自身或其他应用任务的信息,查询即将TCB的内容输出。

(3)挂起任务。挂起优先级为1的任务,则优先级为6的任务开始执行。挂起的任务处于等待状态,只有通过调用任务恢复函数才能恢复。

(4)建立任务。建立优先级分别为5、2和4的3个任务。优先级为5的任务剥夺优先级为6的任务的CPU使用权,优先级为2的任务又剥夺优先级为5的任务的CPU使用权开始执行,优先级为4的任务等待。

(5)删除任务。删除了优先级为2的任务,此刻系统中优先级为4的任务开始执行。

(6)恢复任务。恢复优先级为1的任务,优先级为1的任务剥夺优先级为4的任务的CPU使用权又重新开始执行。

从图6可以看出,硬件实现可以高效完成操作系统任务管理的系统调用的功能。建立任务和删除任务需要3个时钟节拍,挂起任务、恢复任务和查询任务的状态需要1个时钟节拍。任务调度是实时的,只要任务的状态或优先级有一个发生改变,就立刻重新调度。该设计所消耗的逻辑资源较少,降低了开发成本,使其集成组件成为可能。

本文针对传统实时操作系统内核占用系统资源、影响系统实时性的问题,提出了用单独的硬件电路实现实时操作系统中的系统调用和任务调度器的方案。重点给出了采用FPGA实现μC/OS-Ⅱ任务管理模块的过程。仿真结果表明,任务管理的硬件实现保持了系统调用的正确性,同时减少了系统调用的执行时间、降低了处理器系统开销。因此,硬件RTOS的实现,具有一定研究和使用价值。

评论