多媒体数字信号编解码器介绍

TMS320C54xx是TI公司生产的具有较高性价比的DSP系列,采用高性能的改进型哈佛总线结构;内含一个40bit的算术逻辑单元(包括一个40bit的筒形移位器和两个独立的加法器)、软件可编程等待状态发生器以及可编程分区转换逻辑电路;同时带有内部振荡器或用外部时钟源的片内锁相环(PLL)时钟发生器;该DSP带有全双工串行口,支持8位或16位传送;同时带有时分多路串行口、缓冲串行口、16位可编程定时器、8位并行主机接口等;可用外部总线进行关断控制,以断开外部数据总线、地址总线和控制信号;数据总线具有总线保持特性。

本文引用地址:http://www.amcfsurvey.com/article/149288.htm TI公司的TLV320AIC24型多媒体数字信号编解码器则可提供时分复用串行口(SMARTDM),并可用一个先进的TDM格式同步4线串行口以优化DSP的性能,从而实与流行DSP(如C5000、C6000)和微控制器的无缝连接。SMARTTDM提供了连续数据转换和再配置编程两种模式(ADC/DAC和控制数据),可使TLV320AIC24 DSP编码器和DSP数据转换的带宽最大化(只对ADC/DAC数据)。在一般的操作中,它会自动发现串行接口中的编码个数并调整时钟数以与编码数据相匹配。而在TURBO操作中,它可以保持相同的时钟数值,但位转换率最大到达25MHz,允许其他的DSP外围串行器件在相同的采样周期内分离相同的串行总线。TLV320AIC24支持任意基于SMARTDM的器件级联,实现多通道编码(最多可有8路TLV320AIC24编码级联到单个串行口),它所支持的3种串行口配置为单机主、单机从和级联主从模式。

TLV320AIC24还提供两种16位Σ-△A/D通道和16位Σ-△D/A通道,可连接到手机、耳机、麦克风等外部设备;其嵌入的模拟和数字侧音、反偏滤波器、可编程输入输出增益控制等电路楞为麦克风提供前置放大和150Ω负载、硬件/软件控制的掉电模式等功能;TLV320AIC24具有和TMS320C54xx完全兼容的电源电压;其可编程最高采样率达26ks/s(用片上IIR/FIR滤波器)和104ks/s(用IRR/FIR侧通);在8ks/s的采样率下,它们的片上FIR可产生87dB的动态范围(对ADC)和92dB的动态范围(对DAC);ADC和DAC滤波器符合G.711和G.722协议。此外,TLV320AIC24还提供了一个灵活的主机接口(一个可以编程为标准工业I2C总线协议或S2C总线协议的2位串行口)。

2 硬件接口

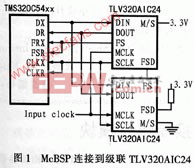

DSP McBSP和TLV320AIC24的接口方式为4路SMARTDM信号,分别为帧同步、串行数据输出、串行数据输入和时钟源,它们分别连接到FSX/FSR、DR、DX、CLKX/CLKR。在级联模式下,DSP可通过主器件的FS端接收帧同步信号,主器件的FDS端连接到第一级从器件的FS端,而将第一级从器件的FSD连接到第二级从器件的FS端,如此类推。最后一级的FSD通过电阻器连接到3.3V电源输入端。图1给出级联TLV320AIC24和DSP的连接方式。

3 软件编程

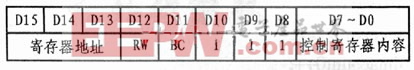

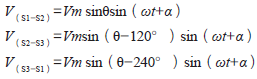

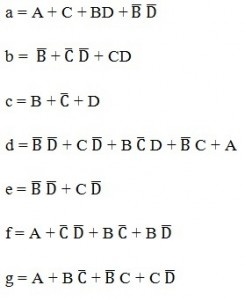

TLV320AIC24的每一个通道都含有6个控制寄存器,可以编程所需的操作模式。在控制帧模式下,通过DIN引脚可以对所有的寄存器进行编程。在一个帧同步延时后,新的配置生效。上电后,TLV320AIC24被默认为编程模式。设置控制寄存器1到第6位可用于转换连续数据模式。如果采用15+1数据格式,那么,把DIN的最低位设置成1可将连续数据传输模式转换成编程设置模式。其格式如下:

其中,D15-D13位为控制寄存器地址,操作时可与位D7-D0所携带的数据一块写入;位D12用于确定对所寻址寄存器的读写;位D11用来确定是否选择广播模式;位D10-D8永远设置为1。

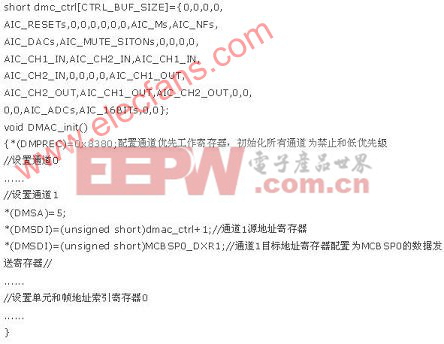

下面给出编码器寄存器的编程例子。其中,DSP通过DMA连接到SMARTDM以对TLV320AIC24进行初始化。DMA是指在不需要CPU干预的情况下,在映射存储区的不同区间传输数据的技术。DMA可支持上存储器、片上外设(包括EHPI8)或是外部设备间无CPU负责的独立数据交换。

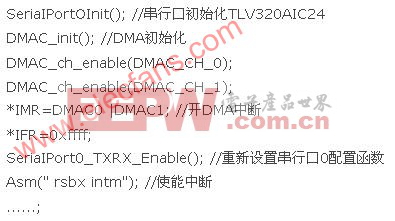

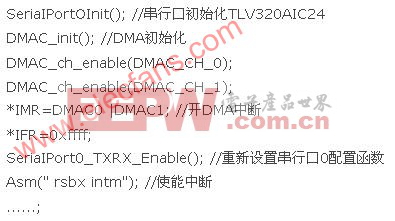

(1)初始化

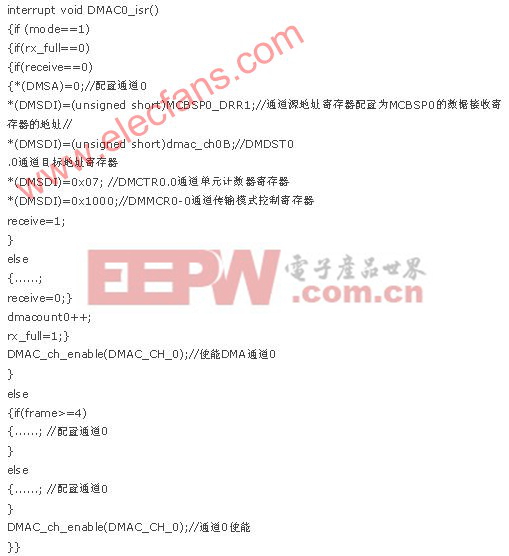

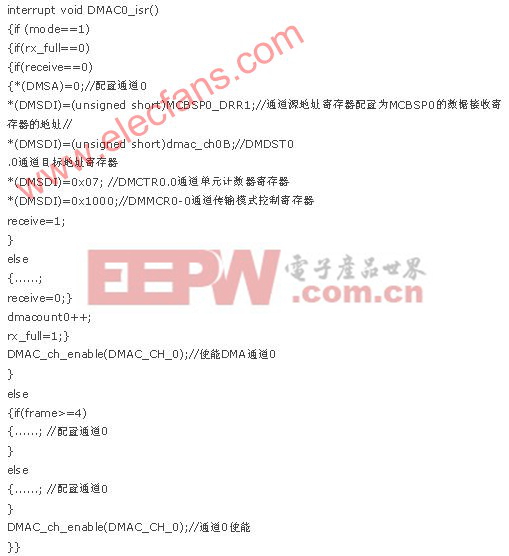

(2)DMA0中断服务子程序,进行数据接收

(3)用DMA初始化TLV320AIC24子程序

评论