CPLD在信号滤波和抗干扰中的应用

单片机应用系统的输入信号常含有种种噪声和干扰,它们来自被测信号源、传感器、外界干扰源等。为了提高测量和控制精度,必须消除信号中的噪声和干扰。噪声有两大类:一类为周期性的;另一类为不规则的。前者的典型代表为50Hz的工频干扰,一般采用硬件滤波,使用积分时间等于20ms的整数倍的双积分A/D转换器,可有效地消除其对信号的影响。后者为随机信号,它不是周期信号,可用数字滤波方法予以消弱或滤除。所谓数字滤波,就是通过一定的计算或判断程序来减少干扰信号在有用信号中的比重,故实际上它是一种软件滤波。硬件滤波具有效率高的优点,但要增加系统的投资和设备的体积,当干扰的性质改变时我们往往不得不重新搭接电路;软件滤波是用程序实现的,不需要增加设备,故投资少、可靠性高、稳定性好,并且可以对频率很低的信号实行滤波,随着干扰的性质改变只需修改软件即可,具有灵活、方便、功能强的优点,但要占用系统资源、降低系统的工作效率。一个传统的实际系统,往往采用软件和硬件相结合的滤波方法,这种结合是在两者的优缺点之间寻找一个平衡点。

硬件抗干扰主要采用隔离技术、双绞线传输、阻抗匹配等措施抑制干扰。常用的隔离措施有采用A/D、D/A与单片机进行隔离以及用继电器、光电隔离器、光电隔离固态继电器(SSR)等隔离器件对开关量进行隔离。

软件抗干扰主要利用干扰信号多呈毛刺状、作用时间短等特点。因此,在采集某一状态信号时,可多次重复采集,直到连续两次或多次采集结果完全一致时才视为有效。若多次采集后,信号总是变化不定,可停止采集,给出报警信号。如果状态信号是来自各类开关型状态传感器,对这些信号采集不能用多次平均方法,必须完全一致才行。在满足实时性要求的前提下,如果在各次采集状态信号之间增加一段延时,效果会更好,能对抗较宽的干扰。对于每次采集的最高次数限额和连续相同次数均可按实际情况适当调整。对于扰乱CPU的干扰,可以采取指令冗余和软件陷阱等抗干扰技术加以抑制。

2 利用CPLD实现数字滤波及抗干扰

这里介绍的采用CPLD实现信号滤波及抗干扰的方法已经在智能仪器泵冲测量仪的开发中得到验证。下面就如何采用CPLD对系统的四路外部传感器脉冲信号和四路按键信号实现滤波、锁存、中断申请等功能进行阐述。

2.1 传感器信号滤波

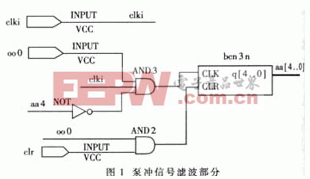

由于要对传感器信号进行数字滤波,CPLD要引入时钟信号。因而我们对CPLD定义一输入端clki,作为数字滤波器的计数脉冲输入端。clki由单片机定时器1定时产生500Hz脉冲。以一路为例,泵冲信号滤波部分如图1所示。

oo0为经电平转换后接近开关输出的信号。当oo0为低电平时,说明泵1未动作,封锁三端与门,时钟信号clki无法通过,计数器bcn3n不计数。同理,当aa4为高电平时,亦封锁三端与门(至于aa4如何变化及作用下文有介绍)。故当oo0为高、aa4为低时,clki接通计数器CLK端。当oo0和clr端任意一个为低时,计数器清零。计数器bcn3n由MAX+PLUSII的文本编辑器编辑,其文本如下:

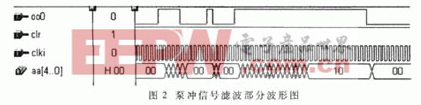

其输出aa4..0等于计数器当前的计数值。Aa4就是aa4..0的最高位当计数值达到10H(十六进制)时,即aa4为高电平时,三端与门封锁,计数器保持10H不变,除非有清零信号。其波形如图2所示。

由波形可知,oo0为高,计数器开始计数。对于小的脉冲,计数器的最高位即aa4为低,认为是干扰信号;只有当aa4为1时才认为oo0的脉冲信号有效,并通过aa4将时钟脉冲阻断,使计数器值不再增加。这样做是为了防止由于oo0的脉冲不定宽,使aa4的电平不定,后面无法进行处理。还应注意的是,把oo0引入了清零信号。当信号有较多毛刺时,若oo0为低时不清零则使计数器不断累加,积累到一定程度,使aa4为1,系统将认为有一有效脉冲信号,产生误动作。

2.2 中断申请信号产生

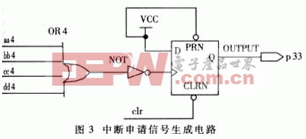

中断申请信号由图3电路生成。

图中四个计数器的最高位接四端或门,只要有一路信号为高,或门输出就为高,并经过非门,输出低电平,接于D触发器的时钟端。D触发器的D端始终为高电平。D触发器为上升沿触发器,若输入D为1,在时钟脉冲的上升沿,把1送入触发器,使Q=1。只有在CLRN端的clr信号有效时,D触发器清零,Q=0。其波形如图4所示。

只要有一路信号为高,D触发器时钟端为低。当所有4路都为低时,时钟端由低变高,在上升沿,Q变为1,发出中断请求信号。

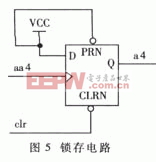

如果多路脉冲信号有重叠,例如有两路信号发生重叠,而中断信号只有在四路都为低时才会产生,因此需要对信号进行锁存。本设计采用D触发器来实现锁存,电路如图5所示。

当aa4为由低变高时,a4变为高电平。由clr信号清零。

2.3 按键消抖及数据输出

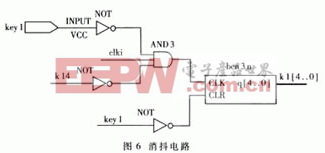

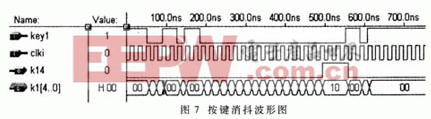

按键的消抖也通过计数器来实现,电路原理图如图6所示。

按键未按下时为高电平,封锁时钟信号。按键按下时,计数器开始计数。当计数器输出最高位为1时,亦封锁时钟信号,防止按键时间不定使需要的k14信号不定。当按键信号为高电平时,对计数器清零,防止计数器累加干扰信号而造成误动作。波形如图7所示。

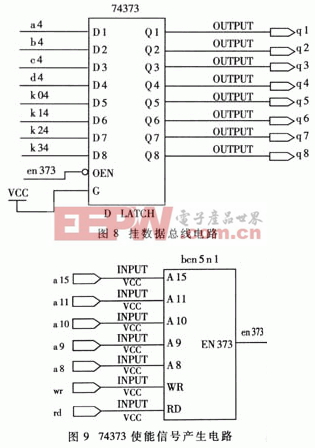

泵冲和按键经处理后的信号a4、b4、c4、d4、k04、k14、k24、k34,经74373挂于数据总线,如图8所示。74373使能信号由图9电路产生。

它采用文本编辑,具体如下:

若单片机发出读81XXH地址中数的信号,则选通此373,读出其数。

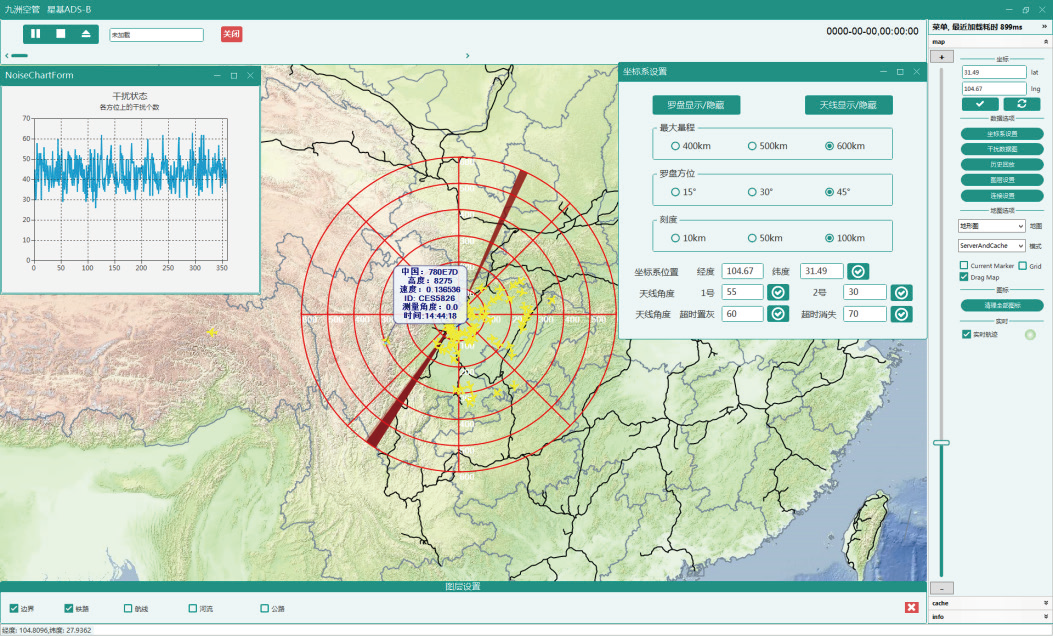

以上介绍了采用CPLD实现数字滤波及抗干扰。该设计已在产品开发中成功应用,效果良好,达到了预期的目的。前面我们已经提到,一个传统的设计,往往在软件滤波和硬件滤波两者的优缺点之间寻找一个平衡点。用我们通常的成语来讲,这样做可以说是扬长避短或取长补短。一直以来,我们都把这两个成语看成是褒义的,不过细细品味一下其中的韵味似乎并不完全是好的代表:发扬长处固然值得称道,但回避短处未必是解决问题的最佳途径,毕竟回避并不能解决问题的本质,哪怕是取其长处来弥补短处,也不是长远出路。应该直接去克服掉短处为佳。采用CPLD则可将软硬件滤波的优点兼而有之,同时将它们的缺点摒弃,从而达到扬长去短的目的。用CPLD实现滤波只占用较少的资源,故可用其实现其它数字电路,同时实现滤波。

电容式接近开关相关文章:电容式接近开关原理

评论