基于北斗二代系统的嵌入式船用导航仪硬件设计

摘要:随着北斗二代系统的研制与建设,在导航领域我国将会从GPS主宰的局面转向为以我国自主研发的北斗二代全球导航系统为主的局面。为了实现北斗船用导航仪更轻便、快捷、低功耗和低成本,提出了一种采用ARM9系列的S3C2440A为处理器的北斗船用导航仪硬件设计方案,详细给出了系统的硬件体系结构和具体的硬件选型及接口电路设计。并对整个系统进行了硬件平台的搭建和测试,给出了北斗信号处理部分的硬件设计电路板,实验表明这种硬件设计可行。

关键词:嵌入式;北斗二代系统;导航仪;硬件设计

目前,随着我国第十颗北斗卫星的成功发射,北斗区域卫星导航系统已完成基本系统建设。北斗卫星导航系统基本上能满足测绘、渔业、交通运输、气象、电信、水利等行业,以及大众用户的应用需求。在加上北斗导航卫星定位系统的ICD的公布,那么对于北斗卫星导航仪的研究势在必行,而我国的北斗导航卫星定位系统同时具备定位与通信功能、可同时解决“我在哪”和“你在哪”等应用优势。但是实际的应用并不理想,主要表现在:1)民用领域应用不充分,未形成产业化的现状;2)用户终端设备价格偏高,在市场上无法与GPS系统形成竞争;3)用户终端设备研制开发滞后,跟不上应用需求。北斗导航在民用领域有着广泛的前景,但影响、制约北斗系统在民用领域获得广泛应用的主要因素就是系统用户终端。而现有的导航仪基本上都是基于FPGA、DSP或者是两者相结合为硬件平台的GPS导航仪,也有比较先进GPS采用ARM作为处理器。在这样的背景下,将ARM处理器运用到北斗卫星导航系统上,研制一种超强信号灵敏度、出众的多路径抑制能力及抗干扰/防欺骗能力;支持多频点、多种升级配置超越主流高端产品;完全自主知识产权;从基带芯片到导航解算完全自主研发,技术支持、产品维护、软件升级、非标定制等均有保障;体积小、功耗低、性能可靠的终端接收机具有重要的意义。

1 系统总体设计方案

本系统的硬件平台为三星公司的S3C2440A微处理器。S3C2440A的核心处理器(CPU)是一个由Advanced RISCMacllines有限公司设计的16/32为ARM920T的RISC处理器。ARM920T实现了MMU、AMBA、BUS及Harvard高速缓冲体系结构。这一结构具有独立的16KB指令Cache和16KB数据Cache。每个都是由8字节的行组成。通过提供一整套完整的通用系统外设,S3C2440A减少整体系统成本和无需配置额外的组件。

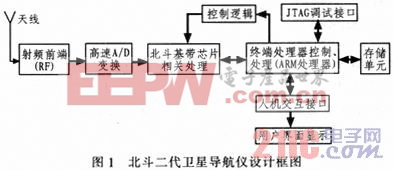

北斗导航接收机主要由射频前端、A/D转换器、基带信号处理和导航解算部分组成。射频前端接收卫星的射频信号,经前置放大器放大后,将信号下变频为中频信号;A/D转换器采样中频信号,把模拟信号量化编码为数字信号;基带数字信号处理部分主要功能为;卫星信号的二维捕获、载波相位和码相位的跟踪,并且测算出伪距;最后导航解算部分采用一定的算法消除模型误差,求解伪距方程,解析出卫星接收机天线的地理位置,从而实现卫星定位。整体设计框图如图1所示。

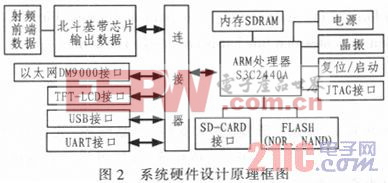

ARM处理器主要是负责对北斗基带芯片数据的响应、处理和控制。北斗基带芯片采用的是HwaNavchip-1芯片,可快速捕获北斗系统B1和B3频点的精密测距码和北斗/GPS卫星的普通测距码,具有较快的捕获速度、极高的动态跟踪范围和测量精度。为降低开发难度,方便二次开发,系统采用的是“核心板+底板”的设计方案,这样可以在核心板不变动的情况下,更改底板的功能组成,以使用不同的功能。同时,由于核心板采用多层PCB板设计,而底板采用双层板即可,从而大大的降低了系统的成本。系统硬件设计原理框图如图2所示。

2 系统硬件电路设计

2.1 核心板电路构成

核心板采用ARM开发板最小系统设计,由S3C2440A处理器作CPU、内存SDRAM、闪存FLASH(NOR FLASH和NANDFLASH)、晶振电路、复位电路和启动配置电路组成。

评论