ARM启动代码的设计分析

ARM体系结构

本文引用地址:http://www.amcfsurvey.com/article/148781.htm目前,ARM系列的通用32位RISC微处理器有ARM7、ARM9、ARM9E、ARM10等多个产品,这些处理器可以工作于7种模式下。除User模式以外的其它模式都叫做特权模式,除User和System以外的其它5种模式叫做异常模式。大部分应用程序都在User模式下运行,当处理器处于User模式下时,执行的程序无法访问一些被保护的系统资源,以利于操作系统控制系统资源的使用,也不能改变模式,否则就会导致一次异常。对于System模式,任何异常都不会导致进入这一模式,而且它使用的寄存器和User模式下基本相同,主要是用于有访问系统资源请求而又避免使用额外的寄存器的操作系统任务。在特权模式下,它们可以完全访问系统资源,可以自由地改变模式。在处理特定的异常时,系统进入对应的异常模式下。这5种异常模式都有各自额外的寄存器,用于避免在发生异常的时候与用户模式下的程序发生冲突。

在任意一种处理器模式中,都使用同一个寄存器来标识当前处理器的工作模式,这个寄存器叫做CPSR(当前程序状态寄存器),它的0~4位用来表示CPU模式,而且在每一种处理器异常模式下,都有一个对应的SPSR(缓存程序状态寄存器),用来保存进入异常模式前的CPSR的值。SPSR的作用就是当CPU从异常模式退出时,通过一条简单的汇编指令就能够恢复进入异常模式前的CPSR,该值保存在当前异常模式的SPSR中。

启动代码类似于电脑中的BIOS,它从系统上电开始接管CPU,依次需要负责初始化 CPU在各种模式下的堆栈空间、设定CPU的内存映射、对系统的各种控制寄存器做初始化、对CPU的外部存储器进行初始化、设定各外围设备的基地址、创建正确的中断向量表、为C代码执行创建ZI(零创建)区,然后进入到C代码。 在C代码中继续对时钟、RS232端口进行初始化,然后打开系统中断允许位。最后进入到应用代码中执行,执行期间响应各种不同的中断信号并调用预先设置好的中断服务程序处理这些中断。整个过程的流程图如图1所示。

图1 启动代码流程图

堆栈初始化

堆栈的初始化要处理的事情是为处理器的7个处理器模式分配堆栈空间。以下以FIQ模式下的堆栈设置为例说明:

ORR r1, r0, #LOCKOUT | FIQ_MODE;把模式放在r1中,LOCKOUT用来屏蔽中断位;

MSR cpsr, r1 ;改变CPU的CPSR寄存器,进入到指定的FIQ模式;

MSR spsr, r2 ;保存前一模式;

LDR sp, =FIQ_STACK ;把FIQ模式下的堆栈起始值赋给当前的SP,FIQ_STACK是分配给FIQ模式堆栈空间(比如说1K字节)的起始地址。按这种方式设置其它模式下的堆栈。

DRAM的初始化根据系统配置信息来决定,因为系统不一定会用到DRAM,但是一定要做SDRAM的初始化。主要的处理内容是ROM和RAM基址的设定、数据总线的宽度、SDRAM的刷新时间等等,这些可以参照S3C4510B芯片的用户手册。特殊寄存器的设置主要是针对I/O口,比方说设定几个I/O位用做系统状态指示灯LED。寄存器的设定主要根据硬件的配置情况而定,值得注意的是由于这段启动代码是烧录到ROM中的,而中断向量必须位于零地址,所以在存储单元没有重新映射之前ROM基址的设定应该为零地址。

拷贝(image)主要是为了提高运行速度,编译生成的映像文件代码从ROM内拷贝到RAM中去,而程序的执行也就在RAM中。当然,启动代码对运行速度的要求不是很严格,所以这个拷贝动作可以不用做,让代码存放在ROM中,代码的执行也在ROM中,而运行中所需要的数据在RAM中。

内存的初始化是为C代码的运行开辟内存区,代码编译后会分为三个区:只读区、可读可写区,

零初始化区。内存的初始化处理的内容是:当只读区截止地址等于可读可写区基址时,把零初始化区各字节清零;当只读区截止地址不等于可读可写区基址时,如果可读可写区基址小于零初始化基址,就从只读区截止地址处开始把数据拷贝到可读可写区基址处,直到到达零初始化基址,然后把零初始化区各字节清零,否则也只用把零初始化区各字节清零。

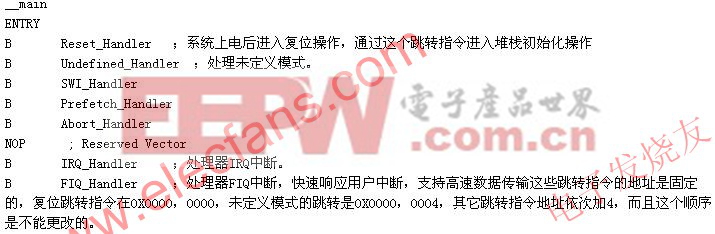

中断向量表是用于处理异常情况的,当发生异常时,首先要保存当前程序的返回地址和CPSR寄存器的值,然后进入到相应的异常向量地址,一般来说在异常向量地址是一个跳转指令,使程序进入相应的异常处理过程。由于中断向量表要位于系统的零地址,当把启动代码烧录到EEPROM中运行时就需要把ROM的地址定义到零地址,所以程序的入口处如下:

评论