QNX 下嵌入式视频监控系统研究

摘要:根据视频监控的特点,设计了一种强实时的嵌入式视频监控系统。系统基于QNX(Quick UNIX)嵌入式实时操作系统,采用异构双核处理器芯片OMAP3530为核心的开发平台,实现了视频的编解码和传输过程。

关键词:QNX;视频监控系统;视频编解码;OMAP3530

引言

嵌入式视频监控系统是当今嵌入式系统发展的热门应用,尤其是数字化视频监控系统越来越受到客户的青睐。目前,嵌入式视频监控系统大多基于Linux操作系统完成,这对于系统CPU是一个不小的开销;同时,系统的稳定性和实时性无法得到很好的保障。本文提出一种基于QNX系统的视频监控系统。QNX(Quick UNIX)是一种实时的微内核操作系统,有利于减小系统CPU开销,并提升系统的稳定和实时性能;用OMAP 3530处理器中的DSP核来完成视频的编解码,有利于提升视频画面质量,提高视频传输速率。

1 系统整体设计

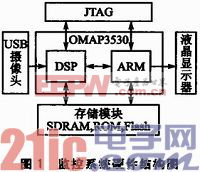

视频监控系统方案是基于开放式多媒体应用平台OMAP设计的。OMAP3530芯片集成了高性能、低功耗的DSP核与控制性能较好的ARM内核,是一种开放式的、可编程的体系结构。系统ARM端负责初始化整个芯片,包括ARM、DSP、TC(Traffic Controller,流量控制器)等的时钟设置,DSP的开启和复位,以及LCD、定时器等各个外设的初始化。DSP端负责视频的编解码。监控系统硬件结构图如图1所示。监控系统主要由OMAP3530芯片、USB摄像头、液晶显示器、存储模块(SDRAM、ROM、Flash)、JTAG构成。USB摄像头获取视频信息后,经OMAP3530部进行视频编解码处理后,存储在存储介质上,或在液晶显示器上进行显示。

1.1 OMAP3530平台介绍

OMAP3530主要由ARM内核、DSP内核及流量控制器TC组成。

OMAP3530采用ARM Cortex—A8核,工作主频最高可达720 MHz。它具有存储器管理单元、16 KB的高速指令缓冲存储器、16 KB的数据高速缓冲存储器和256KB的二级Cache;片内有64 KB的内部SRAM,为液晶显示等应用提供了大量的数据和代码存储空间。ARM内核拥有整个系统的控制权,可以设置DSP、TC以及各种外设的时钟及其他工作参数,控制DSP的运行停止。本设计通过ARM完成对整个视频监控系统的控制和调度。

DSP内核TMS320C64X+采用3项关键的革新技术:增大的空闲省电区域、变长指令和扩大的并行机制。另外,TMS320C64X+内核增加了固化了算法的硬件加速器,来处理运动估计、8×8的DCT/IDCT和1/2像素插值,降低了视频处理的功耗。

流量控制器TC用于控制ARM、DSP以及本地总线对OMAP3530内所有存储器的访问。

1.2 双核之间的通信

系统的实现,需要让ARM核与DSP核实现协调的通信。利用Codee Engine构架,可以实现和管理ARM与DSP双核之间的数据通信。

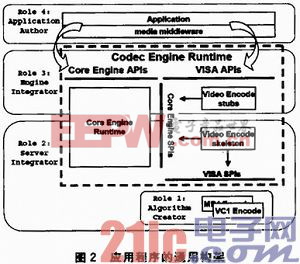

Codec Engine是一组用来配置和运行DSP端的符合xDAIS算法的架构,它把符合xDAIS算法纳入其架构之下,让ARM端的QNX可以调用它提供的VISA标准接口,从而实现ARM与DSP的软件管理。图2是CodecEngine下一个应用程序的通用构架。

图2中,应用程序(Application)或者中间层(mediamiddle ware)调用核心引擎和VISA的API。VISA的API使用存根(Video Encode Stubs)来访问核心引擎SPI(系统编程接口)和构架(Video Encode Skeleton)。这些构架访问核心引擎和VISA的SPI。VISA的SPI访问底层算法。

评论