基于Nios II 软核处理器的SD卡接口设计(一)

摘要:随着FPGA的低成本化和整合资源的不断增强,FPGA在整个嵌入式市场中的份额在不断增加。基于FPGA的NiosII软核以其高度的设计灵活性和完全可定制性在现今电子产品设计及工业控制中扮演着重要的角色。此外,以SD卡为代表的大容量存储卡成为消费电子类产品最重要的存储媒体。基于Nios II软核处理器来读写SD 卡的接口设计在诸多电子系统中的使用也愈来愈多。本文给出了基于Nios II软核处理器的SD卡接口设计方案,并介绍了Nios II的驱动架构,给出SD存储卡在Nios II软核上的驱动程序设计。

本文引用地址:http://www.amcfsurvey.com/article/148032.htm0 引言

Altera公司开发的Nios II是基于可编程片上系统SOPC(System on a Programmable Chip)技术的32 位嵌入式处理器软核。Altera 公司开发的Nios II软核,可以直接放在FPGA中,它体现了把实现产品的全部单元电路集成到一个芯片之内的片上系统SOPC的思想。作为一种具有竞争力的技术,在国外已经有大量的产品使用了这种技术,在国内使用Nios II处理器进行嵌入式系统设计的开发者也越来越多,但是离大规模应用还有距离,应该得到更加广泛的关注。本文在实际的项目中需要使用Nios II来开发存储系统,对于利用Nios II来进行嵌入式系统开发,还有许多工作需要去深入研究本文在进行存储系统项目开发的过程中,完成了基于FPGA的系统硬件软件设计。为了到达系统的设计目标,就需要对Nios II的SOPC技术进行深入的研究。还需要进行uClinux操作系统的移植,基于操作系统的SD卡数据读写,必然就要涉及到怎样编写驱动程序。本文先简单介绍操作SD卡的基本的硬件电路,接着给出了SD卡读写操作和驱动程序设计的基本过程。最后给出了全文的结论,本文给出的方法具有一定的普遍性,和实用性。

1系统硬件结构设计

1.1 SD卡

SD卡(Secure Digitgal Memory Card)即“安全数码存储卡”是由日本松下公司、东芝公司、美国SANDISK 等公司在MMC卡的基础上共同开发研究而推出的,是一种容量大、高性能、安全性好、访问接口简单的存储卡,得到了广泛的使用。使用的范围包括:MP3、数码摄像机和照相机产品、智能手机等消费类电子设备。当前很多微处理器在内部都集成了与SD卡通信的接口电路。

1.2 SD卡的特征

SD 卡的外形和接口触点如图1 所示。外形尺寸分为两种,分别为:24 mm * 32 mm * 2.1 mm 或24 mm * 32mm *1.4mm.

图1 SD 卡的形状和接口

微处理器和SD卡之间的接口电路,要符合一定的约定,这个在SD卡的读写操作中,被称为通信协议。为了适应不同的通信协议,可以设置SD 卡使其工作在不同的通信模式之下。SD卡的通信模式分为两种,一种是所谓的SD模式,另一种是SPI模式。现在SPI通信模式得到越来越多的使用。在处理器和SD卡的通信过程中,和SD卡通信的处理器(称为主机),选择一种通信方式,但在通信的整个过程中不能改变通信模式。SD卡分析复位命令,以确定下面的通信采用什么模式,在接下来的时间内,通信双方要使用相同的通信模式。

当工作在SD模式下时,主机使用SD总线访问SD卡,使用多点总线拓朴结构。这种结构包括一个主机和多个从机(这里是指SD卡)。所有的SD卡共用一个时钟信号CLK、电源和地,命令线和数据线则是属于每一SD卡所专用的。前面说到现在的微处理器都集成有硬件SPI接口,用于板内的芯片之间的操作非常方便。当设定工作在SPI模式下时,主机使用自身所带的SPI总线来访问SD卡。微处理器在第一个发给SD卡的复位命令中配置通信模式为SPI方式,当然在操作SD卡的通信期间,通信模式是不能更改为SD模式的。

1.3 SD卡内部构造

图2是SD卡的内部结构图,主机通过SD卡的接口控制器来控制SD内部的存储单元中的数据。这样设计的目的一方面是把SD卡内部的存储器和外部的操作隔离开来,利于保护内部的数据。另一方面也有利于内部存储器采用更新的工艺,而不影响外部的访问接口。

在使用微处理器来读写SD卡内的数据时,要严格遵循通信协议。首先SD卡的数据传输的基本单位是字节。但是在SD卡的内部是以块为单位来组织数据的。对SD的数据读取操作本质上是以块为单位的。一个块的长度一般是2的幂,比如256字节或者512字节。在具体的一次数据传输中块的长度(以字节为单位)可以在传输数据之前的命令控制字中设置。至于SD卡所允许的块的最大长度可以读取SD卡的寄存器CSD来确定。在SD卡内部有控制寄存器和状态寄存器,其中的4个寄存器中存放着配置信息,比如RCA寄存器中存放本次通信过程中由主机分配的地址。

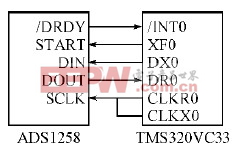

1.4访问SD卡的硬件电路

SD卡采用SPI总线方式与处理器连接,其电路原理如图2所示。

图2 SD 卡接口电路图

1.5 NiosII的构建过程

首先要考虑到的是使用什么样的Nios II,Nios II分为几个等级,有标准内核和高速内核。由于本系统对速度的要求并不高,设计时采用了标准的Nios II内核。在速度和所占用的资源方面具有比较好的折中。采用Altera公司的SOPC Builder工具来进行构建,生成一个Nios II的标准内核。

接着要对选中的Nios标准内核进行配置,这里要考虑的问题是如何如何分配片内存储器和片外存储器的使用。片内存储器的资源是很宝贵的,所以要先确定系统运行所需要的片内ROM或RAM,在满足性能的条件下,尽可能使用较少的片内存储器。

对于一个实际的系统,光有片内存储器一般是不够的,尤其是考虑到要进行嵌入式操作系统的移植,所以还要增加片外存储器。Niso II通过Avalon总线和片外存储器以及外部设备连接。外部存储器件的类型包括SRAM、SDRAM、DDR2、Flash等,外部设备包括UART串行口等。本设计采用SDRAM.

接着是添加PIO端口,定义输入输出端口,主要的目的是用于Nios II读取数字量。Nios II所采用的时钟和FPGA 的时钟密切相关,一般是通过锁相环PLL 把外部输入的时钟进行倍频之后再送给Nios II来作为主频使用,同时外部设备也使用时钟信号。外部时钟信号为25MHz,而经过倍频后为50MHz.

评论