从头到尾构建混合信号高集成度系统(SOC)的步骤(5):电路仿真

Dave Ritter:嗨,Tamara博士,请到烤肉架前来。

本文引用地址:http://www.amcfsurvey.com/article/141904.htmTamara Schmitz:很好。烤蔬菜,还有……那是什么……鲑鱼?

Dave:在柠檬汁中浸过,柠檬就是那边的那棵树上结的,另外还加了我们的秘密调料。再过7分钟左右就可以吃了。

Tamara博士:太好了。这个时间足够你继续讨论设计的硅片方面。啤酒在哪儿?

Dave:在那边的冷却器中。那么你是想知道我们如何从选择制造工艺,决定首先设计哪些模块开始等内容。

Tamara博士:是的。公司使用了许多制造工艺。你们从何处入手?

Dave:选择工艺并不太难。CMOS比双极性工艺便宜(层数少),只要你不需要过多面积来完成。许多CMOS工艺大多是数字电路设计方面的,但我们有模拟技术的很好元器件。这使CMOS成为顺理成章的选择。

Tamara博士:“顺理成章,”嗯?你开玩笑……

Dave:数字电路在越小的工艺中越紧凑,所以你可能认为我们想选择最小的制造工艺。

Tamara博士:这说得通呀。

Dave:不过请不要忘记成本。90纳米、65纳米和更小的工艺更昂贵,因为其制造精度高。同时,这些更小的工艺还具有漏电流,这使设计模拟电路非常困难。这使得100多纳米范围内的工艺更适合该项目。

Tamara博士:所以你在模拟电路质量和减小产品尺寸的能力之间进行了权衡。

Dave:实际上我们是从目标封装开始,所以我们得到约2毫米×2毫米的最大die尺寸。我们想让其10%数字化,由此我们能够估计门电路的数量。如果我们根据我们的样品工作就能完全建立控制算法,那么我们就得到了一个成功设计。

Tamara博士:你们选择从哪个模块开始?掷骰子?扔飞镖?石头-剪刀-布?

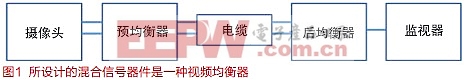

Dave:都不是。该产品在全均衡时的增益几乎达70 dB,所以噪声是关键问题。第一个问题是:我们能否建立一个噪声足够低的均衡器级(输入处的第一个均衡)?所以我构建了一个非常简单的放大器并在仿真器中人为的加入噪声。

有许多因素需要控制:前端MOSFET的跨导gm(增益)使我知道它们的噪声有多高,而额定电流Id使我知道晶体管的运行速度有多快。只需要进行几次快速计算和仿真就能验证我们能否得到数百兆赫的增益带宽积和低于我们2nV/Hz噪声的目标。如果我们达到了这些目标,我们就能获得至少和样品一样的性能。

Tamara博士:好的,那么现在我们有一个均衡器级。接下来呢?

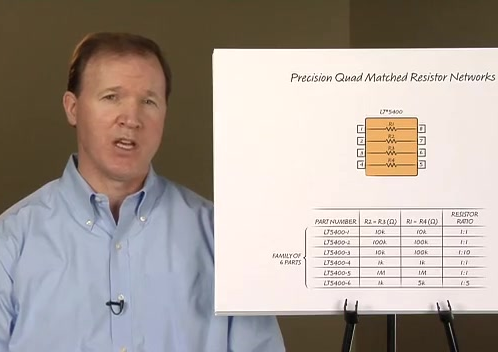

Dave:我们需要控制它。在样品中,这是通过分立数字电位器和多路复用器的组合来实现的。所以我在硅片中构建等效电路并验证了性能(串扰、带宽……等等)。

Tamara博士:这需要多长时间?

Dave:我想噪声和带宽的第一次验证在几个小时内就能完成。其余的大概要几个星期。我添加了多个均衡级和多路复用器来选择它们。在你开发复杂的模块时有许多细节和验证。

Tamara博士:比如?

Dave:每个晶体管都与其周围的晶体管互相影响。需要考虑偏置电压、偏置电流、负载、匹配和温度效应。我喜欢把我的系统分成多个模块,并按照技术规格为每个模块构建一个等效模型。然后设计每个模块,我可以使用来自其他模块的模型进行仿真,以便节省仿真时间。

Tamara博士:所以对于整个均衡器,其余的均衡器级都依次而来。

评论