20nm和3D IC将是积极的产业

过去一年中,Mentor公司实现了10亿美元的营业额。并在20nm设计、3DIC、DFM(可制造设计)、DFT(可测试设计)、SoC验证方面都有很大进展。在北京的MentorForum期间,笔者就目前设计业的一些困惑,询问了Mentor的掌舵人。

本文引用地址:http://www.amcfsurvey.com/article/136884.htm问:随着工艺的演进,每家foundry(代工厂)能支持的设计公司越来越少。例如65nm时,一家代工厂大概可以同时支持60~80个设计。40nm时40~50个,28nm时20~30个,20nm时可能12~16个,因为太复杂,代工厂没有精力了。目前公开说在20nm要去建厂的厂商一共四家:Intel、IBM、三星、TSMC。那么,这对IC设计业会带来哪些影响?

答:每一个新的工艺,都有一个慢慢被接受并提升的过程。到了28/20nm,Foundry在设备的投入确实相当的大。不过我们认为,随着这些资本投入逐渐变为产能后,我们相信会有更多的客户会乐意进入这些先进的工艺,因为成本更加的低廉。除了上述的几家,我们相信UMC(联电)及SMIC(中芯国际)都会很快进入20nm的行列。

另外,任何新的先进半导体制程都是由大批量设计驱动的,像FPGA、无线基带芯片和图形芯片等。由于工艺成熟,代工厂的资源可支持更多的客户,使更多的公司开始做先进技术节点的设计。

28和20nm能够提供独特的差异化。由于代工厂的投资是前代的二三倍,因此接下来的两年会有丰富的晶圆片出现。这些大容量、低成本的晶圆片将鼓励更多企业设计芯片。此外,大批量将导致非常有吸引力的晶片成本,这将使IC设计公司有动力开发较低成本的28nm和20nm芯片。因此,20nm将是非常积极的产业。

问:20nm时代的经济性如何?有人分析过[注1],从0.13微米往90nm走的时候,大概我们还从面积上获得33.6%的降低,从90nm到65nm,还有20.6%,65到45有18%,45到32有10.1%,32到22nm时候,只有3.3%了。估计从22纳米再往下走,成本下降的空间非常有限。摩尔定律还会继续走下去吗?

答:摩尔定律是一种“学习曲线”:每18个月芯片成本减少约50%,芯片内晶体管的数量每18个月翻番。我们认为这种“学习曲线”应能继续。但20nm以后,晶体管的线性尺寸缩减或许将有减缓,不过却可以通过其他的方式维持这一学习曲线的速率。例如FinFET以及3DIC,就是透过三维立体的晶体管形式,或者多芯片堆叠的方法,来满足将来设计对复杂度以及成本的要求。这意味着,,降低每个晶体管的成本仍将遵循“学习曲线”趋势,正如它过去50年中的一样。

问:本土IC设计公司有能力做20nm、3D芯片的还较稀少,Mentor的EDA工具给中国本地带来的意义是什么?这次大会想给本地企业传递哪些新理念?

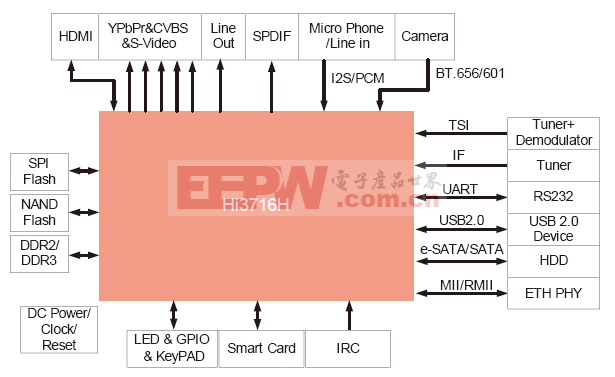

答:Mentor是市场上为3DIC芯片设计提供关键软件的EDA公司。Calibre?提供3DIC所需要的完整验证方案。。此外,Mentor的Tessent?DFT工具能支持所有需测试的堆叠芯片(die)的需求,包括逻辑和存储。Mentor的封装设计软件帮助设计师开发3DIC设计的封装和interposer。可以说,Mentor是3D设计工具的领导者。

在20nm方面,Mentor是第一个向市场推出20nm物理验证工具,主要是Calibre系列。我们还把物理设计和验证技术集成起来,针对20nm所需要的新技术,如doublepatterning(2次曝光)[注2],能够在布局&布线的阶段,就能够预防并解决DoublePatterning可能出现的问题。此外,我们看到20nm技术有利于更复杂的逻辑设计,Mentor的硬件仿真器可以大幅度减少设计的验证时间,能帮助客户提早将产品推向市场。。可以说,Mentor在20nm领域已经提供了完整的方案,领先其他对手。

注1:这段有关工艺与面积的数字来源于《电子产品世界》2012年第9期30页。与Mentor公司所认知的数字不太一致。

注2:doublepatterning(两次曝光):20nm后需要两次曝光或多次曝光。28nm到20nm时,设备不用做大的改变,但是设计手段要变。因为20nm后,设计间距太窄了,一次曝光会使光线无法穿过,或者穿过的光线大大失真。doublepatterning就像两个人坐在一起,为了加大间距,中间可隔开一个位置。因此,人们把一层金属拆成两个mask(掩膜),这样间距加大,光的不良效应就降低。方法是第一次曝光奇数行,第二次偶数行。

评论