采用低功耗28-nm FPGA降低系统总成本

在针对大批量应用开发系统时,要考虑的一个重要因素是成本。有多个方面会影响总体拥有成本,而不仅仅是每个元器件的价格。这包括硅片的功耗要求、材料(BOM)总成本、设计和测试系统的工程师的效能等。选择FPGA供应商很重要,要考虑影响系统成本的方方面面,这体现在整个产品设计周期中。

本文引用地址:http://www.amcfsurvey.com/article/136063.htmAltera® Cyclone® V FPGA通过多种方法帮助设计人员降低系统总成本。设计人员不仅受益于TSMC的28-nm低功耗(28LP)制造工艺,而且还受益于Cyclone V器件系列内置的体系结构,以及Altera设计工具辅助系统所提供的强大的高效能工具。采用Cyclone V FPGA,用户不仅实现了业界最低的总体拥有成本,而且,还获得了型号最全的低成本器件——从25K逻辑单元(LE)到301K LE,以及不到100K LE的唯一28-nm解决方案。

引言

以少胜多——降低成本和功耗,提高效能,使您的产品能够更快的运行。这些棘手的难题是设计工程师目前所必须面对的。好在Altera的28-nm系列产品提供定制方法来解决这些问题。

采用TSMC的28LP工艺以及线键合封装,在所有28-nm FPGA中,Cyclone V FPGA前所未有的同时实现了高性能、低系统成本和最低功耗。Cyclone V FPGA系列有六种目标型号:仅含逻辑的(E)型号、基于3G收发器的(GX)型号、基于5G收发器的(GT)型号,以及这些型号的SoC衍生产品(即,分别是SE、SX和ST),每一型号都含有集成双核ARM® Cortex™-A9 MPCore™应用级处理器。每一器件型号集成了丰富的硬核知识产权(IP)模块,帮助您突出产品优势,以少胜多。与前几代体系结构相比,所采用的先进技术包括,自适应逻辑模块(ALM)、精度可调数字信号处理(DSP)模块、分段式锁相环(fPLL)、硬核存储器控制器,等等,这只是所举的几个例子而已。

与以前的Altera器件系列以及竞争28-nm FPGA相比,您采用Cyclone V FPGA能够大幅度降低总体拥有成本。成本优势源自TSMC的28LP制造工艺,器件丰富的体系结构特性,以及Altera的多种高效能设计工具。Cyclone V FPGA是各类市场应用的最佳选择,包括,工业、通信、军事以及汽车等。

利用TSMC的28LP制造工艺来降低设计成本

Altera在28-nm采用了双管齐下的制造策略,对于需要尽可能提高带宽的系统,使用TSMC的28-nm高性能(28HP)工艺,对于低成本和低功耗应用,则采用28LP工艺。Stratix® V FPGA采用了28HP工艺,而Arria® V和Cyclone V FPGA都采用了LP工艺。对于任何电子系统,降低功耗当然也就意味着降低了运营成本以及总体拥有成本。

根据不同的工艺粒度,用户可以选择最合适的产品来满足他们的需求。TSMC是Altera的代工线合作伙伴,该公司认为:“采用多技术平台上的解决方案,用户能够更好的发挥灵活性优势,推出性能最好的产品。”相对于竞争28-nm产品所使用的“能够满足所有需求”的方法,提供多种产品更适合用户。采用一种制造工艺,无法简单的同时优化实现低功耗和高性能。即使是目的性最强的分级策略也无法解决单一工艺功耗分级会对性能有不利影响,以及性能分级对功耗有不利影响这一两难问题。而且,对于用户而言,分级策略有可能增加系统成本,带来明显的计划和供应风险。

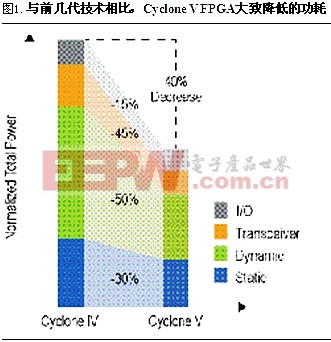

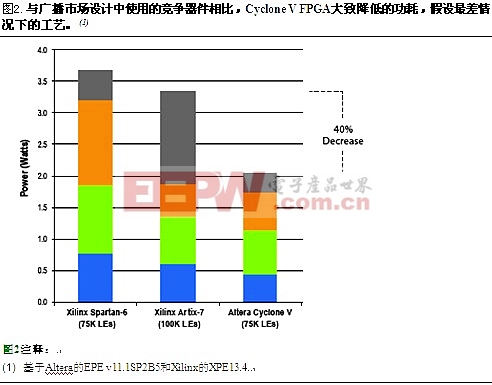

相反,Cyclone V FPGA中使用的成本最优28LP工艺定制满足了低成本和低功耗应用需求。通过采用各种技术,包括使用比28HP工艺更长的栅极沟道等,它同时降低了泄漏电流和动态电流。通过使用比28HP工艺更传统的金属工艺以及线键合封装技术,进一步降低了成本。与倒装焊封装相比,线键合封装使用户在每一型号上节省了大约5美元。Altera的收发器设计专长反映在高速串行接口的高可靠性和低功耗上。在早期功耗估算基准测试中,与Cyclone IV FPGA相比,Cyclone V FPGA展示出明显的低功耗优势(图1),总功耗比Xilinx Artix-7 FPGA低40% (图2)。

评论