基于FPGA的二取二总线数据比较器

摘要:基于FPGA的二取二总线数据比较器实现联锁逻辑运算的两块CPU板总线数据的实时校核。在两条总线数据比较一致且总线数据的CRC校核通过时两个FPGA分别输出互为反相的动态脉冲,板上驱动电路输出信号控制板外供电继电器对联锁系统驱动单元供电,否则通过停止输出动态脉冲在50ms内切断供电继电器。出现校核错时FPGA将比较不一致的两个数据及在对应数据包中的位置等信息反馈给对应CPU板,便于故障分析。通过监测回读信号实现板上驱动电路的实时检测,在驱动电路出现硬件故障时可导向安全。该比较器遵循EN50128,EN50129和EN50126标准流程开发,已通过欧标SIL4级安全认证。

本文引用地址:http://www.amcfsurvey.com/article/134005.htm背景

高速铁路的发展对信号设备性能、稳定性、安全性提出了更高的要求。其中安全性中故障导向安全是设备设计开发中首先要遵循的原则,尽早发现,尽早防范是信号设备安全设计中需考虑的问题。CPU作为控制设备中核心单元一旦运算出错很可能会导致灾难性后果。二取二系统中双CPU校核可有效避免单CPU故障引发的灾难性后果。双CPU校核实现方式包括软件比较和硬件比较。软件比较指CPU通过通信等方式得到对方的数据后各自进行比较,如果比较不一致则通过控制其他外围单元切断输出单元的对外输出使系统导向安全。硬件比较指通过第三方硬件实现两个CPU总线数据的实时比较,不一致时通过第三方硬件可直接切断输出单元的供电,无需CPU参与任何控制(此时故障的CPU可能已不能正常控制其它外围单元)。现场可编程逻辑阵列(Field Programmable Gate Assay,FPGA)通过硬件描述语言进行编程,可完成大规模实时逻辑处理和高速总线接口处理。总线校核需要进行大数据量、快速逻辑处理因此很容易发挥其长处。二取二架构的控制系统安全性高于单机系统因而在铁路系统中得到广泛应用。面向二取二架构的双CPU总线数据比较,我们开发了基于FPGA二取二总线数据比较器,比较器在CPU每个控制周期内完成对总线数据信息的实时校核,如果出现不一致或者非法信息及时切断驱动单元的供电,在最短时间内使系统导向安全侧。

系统方案及硬件实现

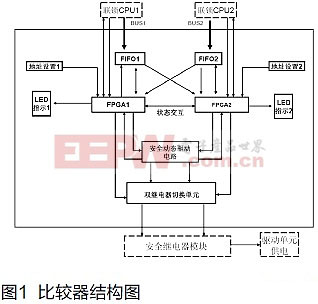

比较器通过两条总线与两块CPU板相连实现总线数据传输和比较相关状态的交互,输出信号驱动板外安全继电器模块实现对驱动单元供电的控制。比较器结构如图1所示,比较器由如下部分构成:FIFO控制器、FPGA单元、安全动态电路、双继电器切换单元、LED指示、地址设置单元。FIFO控制器和FPGA单元由独立的两套构成二取二结构,与二取二CPU板相接合。对于二取二比较器的每一部分有独立的LED指示和总线地址设置单元。安全动态电路和双继电器切换单元本身为二取二结构。

数据比较单元

数据比较单元实现两个CPU板总线数据的同步、独立安全校核,由双套FIFO控制器和双套FPGA单元构成。FIFO控制器用于实现主、从CPU板中总线数据到两个FPGA的传输,其数据存储空间为8192字节,可完成8k字节以下任意大小的总线数据校核。50万门级的FPGA通过内部数字时钟管理模块(Digital Clock Manager,DCM)将外部时钟倍频到40MHz以完成总线数据的高速校核处理。

fpga相关文章:fpga是什么

比较器相关文章:比较器工作原理

评论