三模冗余乘法器的设计与实现

前言

本文引用地址:http://www.amcfsurvey.com/article/128750.htm现场可编程门阵列(Field Programmable Gate Array,FPGA)可通过用户软件编程来配置生成硬件电路,极大提高了电子系统设计中的灵活性和通用性,因而被广泛应用于航天、通信、医疗和工控等重要领域。但在空间环境中,基于SRAM的FPGA容易受SEU(Single Event Upset)和SETs(Single Event Transients)的影响,从而导致系统故障。DMR(Dual Modular Redundancy)和TMR(Triple Modular Redundancy)是系统冗余设计的有效手段,本文设计了一个基于FPGA的三模冗余乘法器。

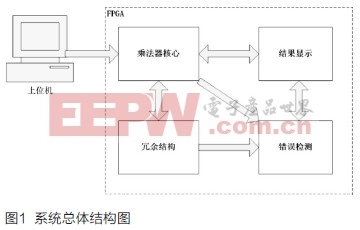

系统总体方案

本系统采用Xilinx公司的Spartan-6 XC6SLX45 FPGA作为系统开发平台,在含有Windows XP操作系统和集成开发环境Xilinx ISE 13.2的PC作为系统的开发环境,开发了一种基于三模冗余的乘法器运算核心冗余系统,系统的结构如图1。

强大的系统开发环境:系统开发环境为含有Windows XP操作系统和集成开发环境Xilinx ISE 13.2的PC机作为系统开发环境。Xilinx ISE系统功能有:1.提供了Verilog语法颜色显示功能,程序很容易查错;2.自行生成程序框架,可以加快系统开发速度缩短系统开发周期;3.多软件协同综合和仿真,ISE内部可以使用集成的仿真功能组件ISIM和网表综合功能组件XST,也可以指定其它公司的仿真和综合工具作为ISE环境的默认开发工具;4.底层布局布线编辑和时序、面积和I/O约束,系统可对生成的布局布线后网表进行自行修改其布局布线情况,以进一步来增强系统性能,通过对系统各种关键路径进行时序约束可以增加系统运行频率,对模块进行面积约束可以减少系统FPGA资源消耗。

评论