基于Virtex-6 PCIE核的DMA控制器设计

总体方案设计

本文引用地址:http://www.amcfsurvey.com/article/128747.htm应用于PCIE总线的DMA方式有两种:系统(system)DMA和总线主控(bus master)DMA。系统DMA比较少见,并且只有较少的北桥芯片和操作系统支持其应用;总线主控DMA是PCIE系统目前为止最常用的控制方式。本文参考了Xilinx的应用设计:应用于Virtex-6 FPGA PCIE核的DMA设计不完整,缺少数据FIFO,且复位后只能完成一次中断的读写;应用于Virtex-5 FPGA PCIE核的DMA设计,可以实现ML555开发板上DDR2内存与PC端内存间数据交换。但应用于Virtex-5和Virtex-6 FPGA的PCIE核用户端口差别较大,故本文基于Virtex-6的设计,借鉴Virtex-5的思想,实现块式DMA的设计。

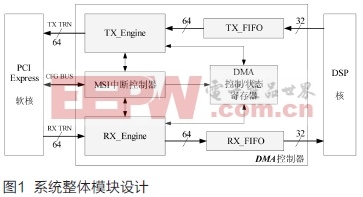

FPGA片上程序设计主要包括3部分:PCIE软核,DMA控制器和DSP应用。PCIE软核通过Xilinx公司ISE 设计套件的CORE Generator软件配置,该IP核集成了传输层(TL)、数据链路层(DLL)和物理层(PL)协议,其应用层接口包括传输接口、配置接口和中断接口等,用于PCIE核和DMA控制器之间的数据传输和寄存器配置;DSP核是用户开发的应用程序。本设计整体模块结构如图1所示。

DMA控制器设计

本文DMA控制器结构框图如图1所示,主要包括发射引擎、接收引擎、DMA控制/状态寄存器、MSI中断控制器和发射/接收FIFO。为描述方便,本文定义写操作和发送(TX)为FPGA将数据发送至PC端存储器;读操作和接收(RX)为FPGA接收来自PC存储器的数据。

评论