引领28nm FPGA“智”造时代

Zynq-7000产品系列,集基于ARM Cortex-A9 MPCore处理器的完整片上系统(SoC)和集成28nm可编程逻辑为一体,专为要求高处理性能的嵌入式系统而构建,其目标市场包括汽车驾驶员辅助、智能视频监控、工业自动化、航空航天与军用、广播以及新一代无线应用等。

本文引用地址:http://www.amcfsurvey.com/article/127380.htmISE 13提升效率

当今芯片的架构设计/平台成为必然,包括芯片和软件两部分,软硬结合是架构设计最主要的特征。因此,7系列的推出也伴随着软件开发环境的创新。

赛灵思ISE Design Suite 13设计套件,专门针对最新28nm 7系列FPGA,ISE 13致力于让客户最大限度地利用有限的时间和设计资源实现最大的生产力。

ISE 13在CORE Generator系统中提供了AXI(Advance extensible Interface,先进的可扩展接口)互联支持,以构建性能更高的点对点架构。设计团队如果构建了自己的符合AXI协议的IP(知识产权),那么就能利用可选的AXI BFM(总线功能模型)验证IP仿真AXI互联协议,从而可轻松确保所有接口处理都能正确运行。赛灵思ISE 13还为设计人员带来了强大的PlanAhead设计环境和分析工具。

堆叠硅片互联:FPGA迈向3D

超越摩尔定律

长期以来,摩尔定律因其惊人的准确性,成为半导体行业发展的准则和轨迹。但是,单单依靠摩尔定律,可控的功耗和代工厂良率无法满足市场对资源无止境的需求。为此,赛灵思找到了一个新的思路—堆叠硅片互联(SSI)技术,加上与伙伴合作的技术/工艺,使赛灵思成为挑战3D(三维封装)FPGA的先锋,可以为市场推出一种能够应对当下挑战的可行的可编程解决方案。

2011年10月,赛灵思横空出世了堪称世界最大容量FPGA—Virtex-7 XC7V2000T,为业界首批堆叠硅片架构的FPGA产品,其包含68亿个晶体管,共200万个逻辑单元(相当于2000万个ASIC门)。据赛灵思公司全球高级副总裁、亚太区执行总裁汤立人介绍,Virtex-7 XC7V2000T不仅仅是晶体管数最大的FPGA产品,同时也是截至目前半导体历史上集成晶体管数最多的单个IC—这不仅仅是摩尔定律的延续,更是对摩尔定律的超越。

因此,3D FPGA有望在一些领域内逐步取代ASIC和ASSP。汤立人称,Virtex-7 2000T FPGA标志着赛灵思创新和行业协作史上的一个重大里程碑。对于客户而言,其重大意义在于如果没有SSI技术,至少要等演进到下一代工艺技术,才有可能在单个FPGA中实现如此大的晶体管容量。现在,有了Virtex-7 2000T FPGA,客户能立即为现有设计增添新的功能,不必采用ASIC,单个FPGA解决方案就能达到3~5个FPGA解决方案的功能,因而可大幅降低成本。或者现在就可以开始采用赛灵思的最大容量FPGA进行原型设计和构建系统仿真器。这和通常的更新换代速度相比,至少可以提前一年时间。

SSI技术

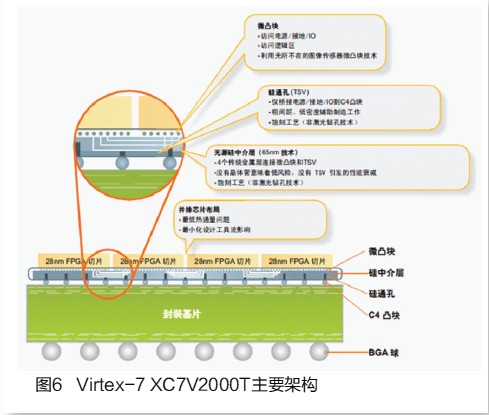

新的SSI技术使赛灵思能够为当代工艺技术带来下一代的高密度性能,有望改善容量和集成度,节约PCB(印制电路板)板级空间,进一步提高产量。Virtex-7 XC7V2000T主要架构如图6所示。

1. FPGA核心

最上层为FPGA核心层,采用4个含50万逻辑单元的28nm FPGA核心(切片)肩并肩排布,而非采用2个含100万逻辑单元的或单个200万逻辑单元的FPGA核心。原因在于当IC的规模和复杂度不断提升的同时,其良品率将受到一定程度的影响。此种设计能在保证良品率的同时,提高逻辑单元数目。

2. 微凸块

微凸块并非直接连接于封装,而是互联到SSI技术最关键的部分——无源硅中介层,进而连接到相邻的芯片。这种设置方法能够避免微凸块受到静电放电的影响,从而带来巨大优势。通过芯片彼此相邻,并连接至球形栅格阵列,该器件避免了采用单纯的垂直硅片堆叠方法出现的热通量、信号完整性和设计工具流问题。

3. 硅中介层

SSI技术设置了一个65nm工艺的无源硅中介层,其本质类似于IC内部的互连线,在芯片外部实现了芯片间的直接互联。这样解决了传统方式所带来的问题,将单位功耗芯片间连接带宽提升了100倍以上,时延减至五分之一,也不会占用任何高速串行或并行I/O资源。而且,硅片中的芯片连接数量大大超过系统级封装。而且这种方法的最大优势还在于节能性。通过SSI技术连接芯片,其功耗远远低于通过大线迹、封装或电路板连接的方式。

评论