引领28nm FPGA“智”造时代

2010年,TSMC已为客户的28nm FPGA提供了先进的硅穿孔(TSV, Through Silicon Via)以及硅中介层(Silicon Interposer)的芯片验证(prototyping) 服务。凭借TSMC研发的TSV及与IC制造服务业者兼容的晶圆级封装技术,TSMC承诺与客户紧密合作开发符合成本效益的2.5D/3D(2.5维/3维)集成电路系统整合方案。

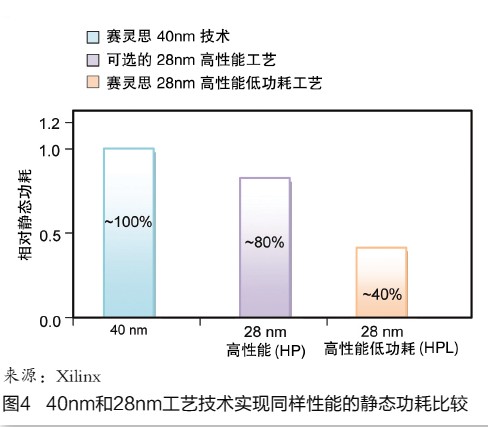

本文引用地址:http://www.amcfsurvey.com/article/127380.htm如果用一个简单的量化标准来衡量28nm和40nm工艺的区别的话,集成度是传统40nm工艺的两倍。通过将更多功能单元集成在单一的系统级芯片上,企业可以大幅降低终端产品成本,并且可以制造出更小、更薄的产品。与传统的40nm工艺相比,在指定速度下,28HPL的功耗最高可以减少一半(图4),部分设计的待机功率更可以低至30%,而速度上最高可以有将近80%的提升。

赛灵思的全新FPGA就是基于TSV技术的28nm新产品,赛灵思亚太区销售及市场副总裁杨飞坦言这得益于28nm工艺技术——28nm高性能低功耗工艺(28HPL)。赛灵思推出了统一的Virtex架构,将整体功耗降低一半且具有高容量(200万逻辑单元)的7系列FPGA产品,不仅能实现出色的生产率,解决 ASIC 和 ASSP 等其他方法开发成本过高、过于复杂且不够灵活的问题,使 FPGA 平台能够满足日益多样化的设计群体的需求。

设计挑战

新工艺带来新竞争优势的同时,将许多设计和制造上的挑战也带给业界,为此,要求设计者与EDA(电子设计自动化)和晶圆厂之间保持良好的合作以应对全新的设计和制造挑战。

谈及SoC(系统级芯片)设计师在新的节点中将会遇到的工具和方法的转变, Synopsys公司战略联盟总监Kevin Kranen认为,新节点面临的挑战各不相同:32nm和28nm的EDA工具需求相同,其所面临的主要挑战包括以下几方面:

⒈由于SiON栅极介质厚度过薄难以控制,在降低栅极漏电和阈值变异性方面的挑战;

⒉在193nm光刻基本限值下的挑战;

⒊用于参数提取的新工艺拓扑结构建模方面的挑战;

⒋管理参数异变性,尤其是在签核期间异变性的挑战。

评论