2.5D IC封装超越摩尔定律,改变游戏规则

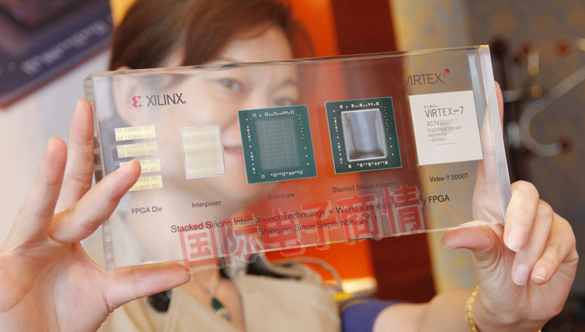

近日,有两家公司同时发布了在芯片封装方面的革命性突破:一个是意法半导体宣布将硅通孔技术(TSV)引入MEMS芯片量产,在意法半导体的多片MEMS产品(如智能传感器、多轴惯性模块)内,硅通孔技术以垂直短线方式取代传统的芯片互连线方法(无需打线绑定),在尺寸更小的产品内实现更高的集成度和性能。另一个则是赛灵思宣布通过堆叠硅片互联 (SSI) 技术,将四个不同 FPGA 芯片在无源硅中介层上并排互联,结合TSV技术与微凸块工艺,构建了相当于容量达2000万门ASIC的可编程逻辑器件。虽然同样是基于TSV技术,前一种垂直堆叠业界称为3D封装;后一种互联堆叠称为2.5D封装。这两种不同TSV封装技术的成功量产商用,将会带来一种新的游戏规划——在摩尔定律越来越难走、新的半导体工艺迈向2xnm越来越昂贵的今天,封装上的革命已是一种最好的超越对手的方式。

这里要解释一下为什么一个是3D封装,一个叫2.5D封装。“目前业界已达成一个观点,3D是指垂直的堆叠,把多颗主动IC用微凸快(micropum)和硅通孔技术连在一起,微凸快是一种新兴技术,中间有非常多的挑战。比如两个硅片之间有应力,举例来说,两个芯片本身的膨胀系数有可能不一样,中间连接的微凸快受到的压力就很大,一个膨胀快,一个膨胀慢,会产生很大的应力。第二,硅通孔也会有应力存在,会影响周围晶体管的性能。第三是热管理的挑战,如果两个都是主动的IC,散热就成为很大的问题。所以对于真正的3D封装,行业需要解决上面三个重要挑战。” 赛灵思公司全球高级副总裁,亚太区执行总裁汤立人解释,“目前能实现3D封装的只是Memory芯片。意法半导体的MEMS能实现3D封装,因为它面临的发热等问题小一些,但对于移动终端来说,器件尺寸会大大减小,这也是一个趋势。从目前掌握的情况看,要实现不同的复杂逻辑IC之间的真正3D封装,至少还需要2-3年的时间。”

他接着解释 2.5D的方式:“我们联合TSMC和Amkor等产业链伙伴,采用的2.5D方式,多颗主动IC并排放到被动的介质上。因为硅中介层是被动硅片,中间没有晶体管,不存在TSV应力以及散热问题。通过多片FPGA的集成,容量可以做到很大,避开新工艺大容量芯片的良率爬坡期,并因为避免了多片FPGA的I / O互连而大幅降低功耗,比如此次我们推出的集成四片FPGA的Virtex-7 2000T功耗小于20W,容量相当于ASIC的2000万门。如果是4个单片FPGA分开采用,加起来的功耗远远大于这个数,可能会是几倍的数值。”

评论