FPGA与GPS_OEM板的UART设计

引言

本文引用地址:http://www.amcfsurvey.com/article/123978.htmUART(标准异步接收器/发射器)得到了相当广泛的应用,它允许串行链路上进行全双工通信。一般使用通用的UART接口芯片,但这种芯片存在电路复杂、成本高,降低了系统的可靠性和稳定度,由于结构和功能的相对固定,因而我们不能根据自己的设计需要去进行剪裁和移植。而日益成熟的SOPC(Silicon on Programmable Chip,系统可编程芯片)技术要求将整个设计功能集成到一块或几块芯片中,本文通过对UART功能的分析,提出了在FPGA上集成UART功能模块,增强了设计的灵活性,简化了电路,并通过有限状态机来描述核心功能控制逻辑,从而提高了整个系统的稳定性和可靠度。基于这种思想,本文提出了一种使用VHDL[1]语言开发UART核心功能的方法,将UART模块嵌入到FPGA芯片,实现了FPGA与GPS_OEM板之间的数据通信,为FPGA采集并处理GPS_OEM板数据提供基础。UART所有功能的实现全部采用VHDL硬件描述语言来进行描述。设计、综合、仿真在QUARTUS II9.0软件开发环境下实现。

系统设计

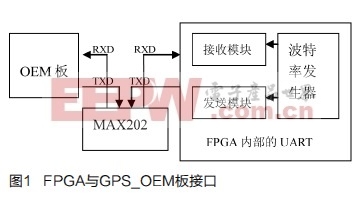

由于FPGA接口采用TTL电平,而OEM[2]板的串行通信采用RS-232标准电平,故需电平转换,电平转换接口可以通过MAX202[3]片来实现。GPS25LP[4]两个串行口,其端口1可用来输入差分修正信息和输出卫星的原始测量信息,而端口2则用来输入设定语句和输出定位语句,因此,只需将FPGA接口与GPS25LP串行口2对应连接即可。其接口电路如图1所示。FPGA的全局时钟Global_clk由24 MHz的晶振产生。

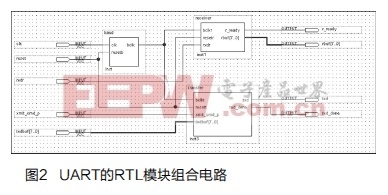

UART电路由波特率发生器、发送模块和接收模块3部分组成。UART的RTL(寄存器传输级)模块组合电路如图2。波特率发生器为发送模块和接收模块提供时钟信号,以实现数据的异步可靠传输。

假定本方案设计的UART数据格式为:数据位为8位、波特率可选、不设奇偶校验位、1位停止位,异步通信的过程如下:GPS_OEM板产生发送串行数据,由MAX202的TXD端输入,经过MAX202进行电平转换由FPGA串口接收模块的RXD端进入,进行串并转换得到8位位宽数据总线,该数据由FPGA的其他模块进行处理;FPGA产生发送的8位并行数据,数据由8位数据线进入FPGA串口发送模块,进行并串转换后由TXD输出到MAX202的,经过MAX202电平转换发送至GPS_OEM板。

fpga相关文章:fpga是什么

晶振相关文章:晶振原理

评论