MathWorks HDL工具新添Xilinx FPGA硬件验证功能

—— 启用 FPGA 在环仿真以使用Simulink对Xilinx FPGA开发板上的HDL代码进行验证

MathWorks 日前宣布适用于 Xilinx FPGA 开发板且新添了 FPGA 在环 (FIL) 功能的 EDA Simulator Link 3.3 面市。FIL 使工程师们能够在使用 Simulink 作为系统级测试台架的同时,以硬件速度验证其设计。

本文引用地址:http://www.amcfsurvey.com/article/120314.htmEDA Simulator Link 支持 HDL 验证选项全集使用在 MATLAB 和 Simulink 中创建的算法,而 FIL 的引入则进一步补充了这一全集。基于 FPGA 的验证不仅提供了比 HDL 仿真器高得多的运行时性能,而且增强了算法的实际应用效果。

主要的产品功能包括以下能力:

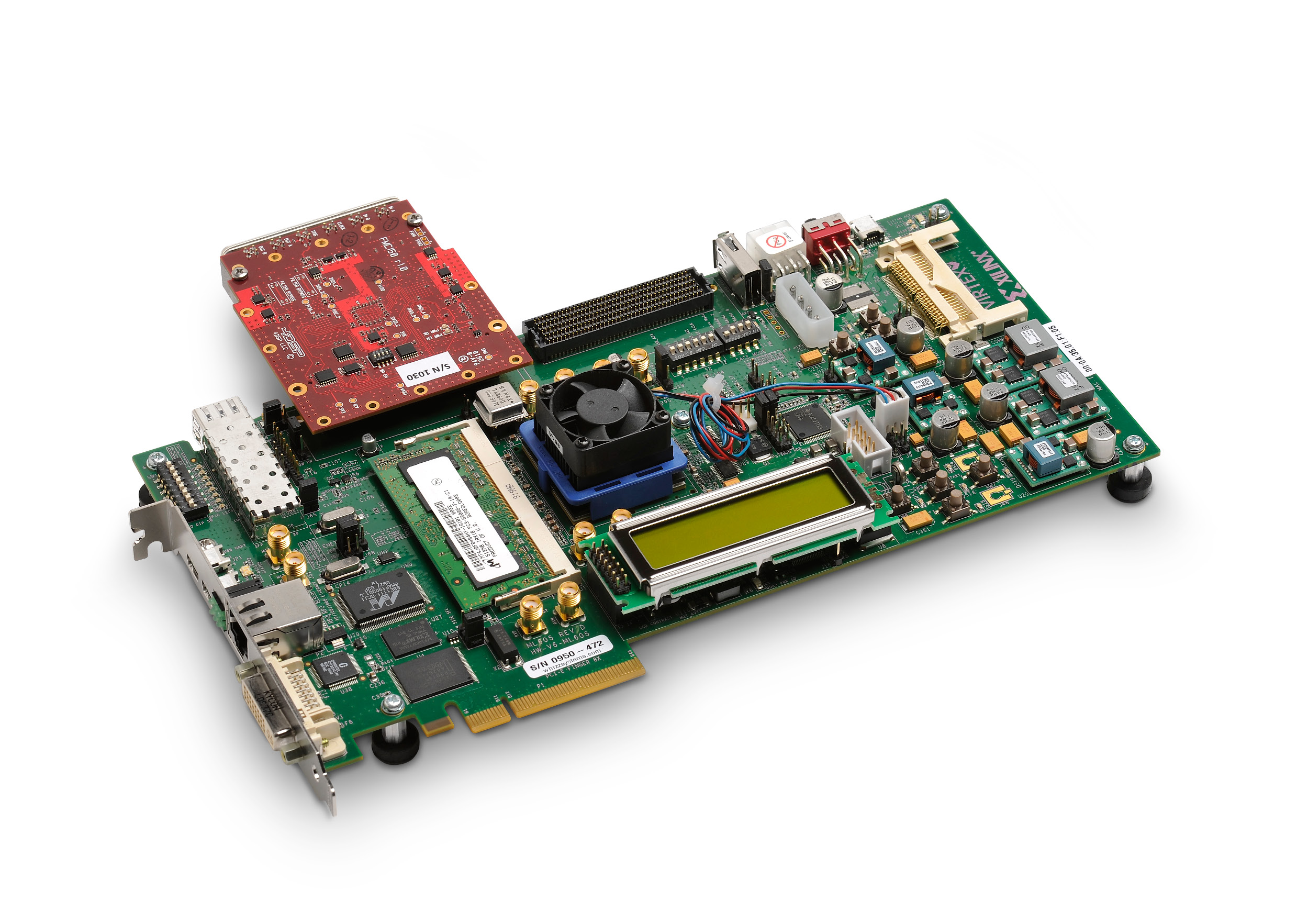

• 使用适用于 Spartan 和 Virtex 类设备的 FPGA 开发板(包括 Virtex-6 ML605 开发板),验证 MATLAB 代码和 Simulink 模型的 HDL 实现。

• 使用 Mentor Graphics ModelSim、Mentor Graphics Questa 和 Cadence Design Systems Incisive Enterprise Simulator 的协同仿真,验证 MATLAB 代码和 Simulink 模型的 HDL 实现。

• 生成适用于 SystemC 虚拟原型环境的 TLM 2.0 组件。

图注:

EDA Simulator Link 为 Xilinx Virtex6 和 Spartan6 FPGA 开发板提供了 FIL 仿真支持。

评论