MIPS -- 适用于MCU的处理器

1.简介

本文引用地址:http://www.amcfsurvey.com/article/118393.htmMIPS科技是知名的致力于开发和授权高性能处理器内核以及32位和64位架构的公司。作为数字家庭和网络领域中的市场领先者,MIPS架构亦已在32位微控制器(MCU)领域大量应用,与基于ARM架构的内核产品相比,可提供性能更高、功能更丰富且功耗更低的解决方案。

MCU广泛应用于各种市场应用,包括以工业、自动化、汽车、消费电子以及以无线通信为代表的前沿技术。在这些类型的应用中,MCU的运用使得对嵌入式处理器内核的需求不断增长,同时要求嵌入式处理器内核提供更高效的性能、更快的实时响应、更低的功耗以及广泛的生态系统支持。这些需求来源于各种新挑战,包括需要运行更复杂的RTOS控制软件,以及集成更高速的通信接口与更复杂的接口。

32位MCU正逐步为下一代应用提供解决方案。Semico Research Corp.预测32位MCU产品出货量的年复合增长率(compound annual growth rate,CAGR)在未来几年为18%,在2014年出货量将达到25.73亿件。

选择正确的处理器架构是使MCU产品达到性能、成本和上市时间目标的关键决策条件。本文将对MIPS®处理器内核中实现的设计功能进行介绍,这些功能对其达到业界领先的性能起到了关键作用。此外,我们将对基于MIPS和ARM架构(两种最流行的嵌入式处理器架构)的MCU设计解决方案进行比较。我们的分析将会证明,MIPS提供的解决方案性能更高、功耗更低且具有更先进的功能和卓越的开发支持。

2.MIPS架构

MIPS架构于20世纪80年代早期在斯坦福大学诞生,是基于简洁的加载/存储RISC(精简指令集计算)技术的架构。RISC技术实现了简单但全面的指令集,并使用深度指令流水线,与以前的CISC(复杂指令集计算)架构相比,可获得更快的执行速度和更高的性能。相比较而言,ARM架构基于混合的RISC/CISC架构,其设计复杂,且实现高级别性能的能力有限。

自1985年第一块MIPS处理器(R2000)问世以来,MIPS架构始终在不断地完善。指令集架构(Instruction Set Architecture,ISA)在经过几次修订后得到扩展,其性能也相应提高。目前版本包括32位和64位的MIPS32Ò和MIPS64Ò架构。除了基于MIPS32开发一系列32位处理器内核之外,MIPS还对MIPS32和MIPS64架构进行授权。这些架构的授权用户包括Broadcom、Cavium Networks、LSI Logic、NetLogic Microsystems、Renesas Electronics、Sony、Toshiba、中科院计算所和北京君正等,它们正积极地推出适用于数字家庭、网络、单片机和其他应用的MIPS-Basedä产品。这些基于MIPS的产品合计年出货量超过6亿件。

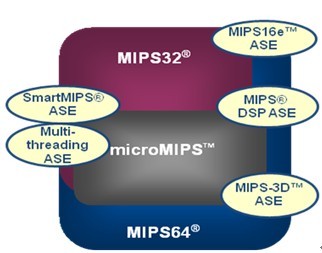

图1:MIPS科技架构和ASE

图1显示了市面上MIPS架构系列的组成部分。标准MIPS32/64架构可通过可选的特定应用扩展(Application Specific Extension,ASE)来扩充功能,包括MIPS16e®、SmartMIPS®、DSP、3D和多线程。这些ASE旨在分别针对特定应用提供增强功能。例如,DSP ASE通过增强软硬件功能,加速了MIPS处理器内核设计中的信号处理功能。类似地,MIPS16e是将“最经常”使用的MIPS32指令解码为相应的16位等效指令后所组成的指令集。与MIPS32相比,MIPS16e可压缩应用程序代码,使其占用较少的存储器容量,同时通过减少存储器带宽和缩短执行时间来保持高性能。图1中所示的每种ASE均有助于提高目标处理器内核的特定于应用的性能。

MIPS科技最近推出的microMIPS™是一套完整独立的指令集架构(ISA),同时包含16位和32位指令,旨在使软件代码密度和执行吞吐量最大化。microMIPS可至少将代码长度减少30%,并且执行性能几乎与MIPS32相同。microMIPS 集成于MIPS32 M14K™和M14Kc™处理器内核中,这些内核是为MCU和嵌入式控制器SoC的设计而开发的。

通过MIPS32/64架构中实现的先进技术及其处理器内核中包含的先进功能,MIPS ISA标准软件平台超越了竞争对手的解决方案并提供了更大的灵活性和持续改进的空间。

2.1 MIPS架构性能

从高端多核解决方案到紧凑型内核,所有MIPS处理器内核均基于相同的高性能MIPS32基础架构进行设计。

MIPS内核的主要性能改进来自于内核执行单元的功能增强,通过实现较长的流水线级数、超标量和多线程微架构来提高处理器的最大工作时钟频率。通过在标准架构中加入高速存储器接口、高效缓存控制器、存储器管理单元、大量寄存器组以及浮点加速器等设计功能来获得附加性能。

MIPS32架构标配32个通用寄存器(General Purpose Register,GPR),其中每个寄存器的位宽为32位。在芯片设计阶段可以对MIPS配置更多的通用寄存器组(每组32个),用作附加数据存储或者分配给专用向量中断控制器逻辑的“影子寄存器”,在传统软硬件方法的基础上可显著减少中断延时和现场切换时间。

利用硬件乘除单元(Multiply Divide Unit,MDU)以及多个带符号/无符号乘法、除法和乘加(MAC)指令的软件支持,可有效提高MIPS32架构的信号处理性能。MIPS架构对MDU采用独立的流水线,使其可以与整数流水线并行工作。

评论