ADF4108在宽带X波段频率合成器中的应用

电路设计、噪声分析及仿真

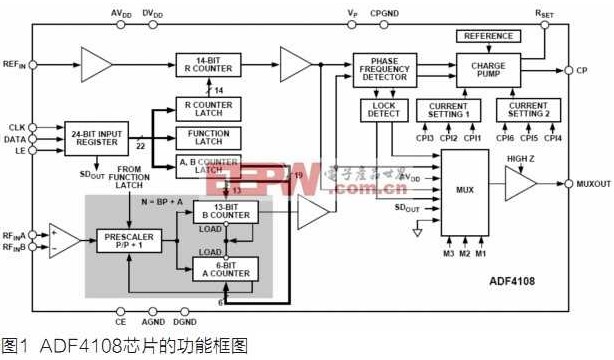

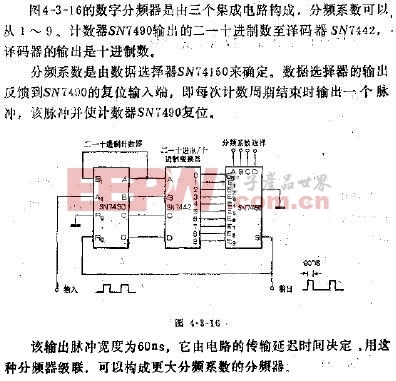

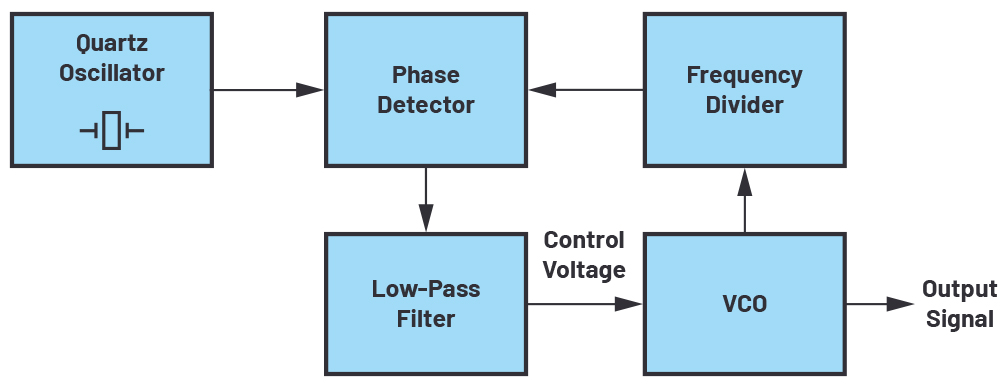

本文引用地址:http://www.amcfsurvey.com/article/117111.htmADF4108主要由一个低噪声数字鉴相器(PDF)、一个精密电荷泵、一个可编程参考分频器、可编程A(6bit)及B(13bit)分频计数器和一个双模分频器(P/P+1)构成。在这里,随模式控制高、低电平的不同,双模分频器采用两个不同的分频模数P+1和P。双模分频器的输出同时驱动两个可编程分频器,他们分别预置在A和B(A<B),并进行减计数。在除A和除B分频器未计数到零时,模式控制为高电平,双模分频器输出频率为f0/(p+1)。在输入A(P+1)个周期之后,除A分频器计数到零,将模式控制变为分频器前面的与门使其停止计数。此时,除B分频器还有B-A个数,双模分频器的模数变为P,输出频率为f0/p。再经过P(B-A)个周期,除B分频器计数到零,输出低电平,再将两计数器重新置为A和B,同时将模式控制恢复为高电平。通过这一完整的周期,合成器的分频比为:N=(P+1)A+P(B-A)=PB+A,频率分辨率为fr。另外,R(14bit)参考分频器为PDF提供参考频率fREF,再加上外部的环路滤波(LF)、压控振荡器(VCO)就构成了一个完整的锁相环(PLL)。

压控振荡器输出的信号经N次分频后送入鉴相器中作为一路鉴相信号,参考晶振输出的标准信号经参考分频器R次分频后送到鉴相器中作为另一路鉴相信号。鉴相器的输出反映两路鉴相信号相位误差特性的电流序列脉冲,经电荷泵的作用输入到低通滤波器中,低通滤波器将电流转换成VCO的控制电压,同时对噪声及鉴相输出的纹波等干扰进行抑制,鉴相器内部还有一个可编程延迟单元,用来控制翻转脉冲的宽度,这个翻转脉冲保证鉴相器的传递函数没有死区,因此,降低了相位噪声和参考杂散。VCO输出与其输入端控制电压相应的工作频率。

ADF4108最大的特点是工作在高频,设计的锁相环路具有宽带宽,从而在X波段频合器中省掉了倍频器,消除了倍频器带来的谐波、杂波及噪声干扰(倍频器对系统的噪声恶化公式为:10logN,其中N为倍频次数,即每增加一倍频率就会带来3dB的噪声),这样有利于简化系统电路、提高系统性能及降低系统成本。ADF4108能通过芯片的数字串口接口对A、B、R及P等寄存器进行预置和改变,从而可方便地获得不同的输出频率。其功能框图如图1所示。

噪声分析

对于PLL整个系统而言,其总相位噪声也是我们关心的一个重要问题,它和很多因素有关。

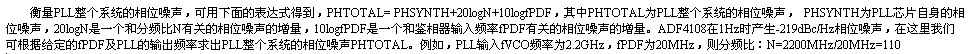

频率合成器的相位噪声和10logfPDF有关,对于每一个2fPDF频率而言,其相位噪声将减小3dB。然而VCO的输出被分频,它的相位噪声符合20logN的规律(其中N为分频比,N=BP+A),因此,对每一个N=2值来说,将增加6dB相位噪声。例如4fPDF频率,fVCO除以4得到fOUT的输出。一方面,在4fPDF的频率下相位噪声减少6dB;另一方面,因为fVCO除以4而增加了12dB的相位噪声,总的结果将增加6dB的相位噪声。

![]()

评论