基于FPGA的PPM系统设计与实现

摘要:给出了脉冲位置调制(PPM)系统的设计方案,并基于FPGA通过简明的Verilog代码实现了该设计,时序仿真结果验证了所设计的系统能够满足PPM系统的要求,并在满足一定性能需求的情况下消耗了较少的逻辑资源。

本文引用地址:http://www.amcfsurvey.com/article/113812.htm引言

作为一种新型的通信技术,脉冲位置调制(PPM)系统依靠其编码简单、传输效率高等优点,已广泛应用于超宽带移动通信、光通信、机载设备的空地数据链等诸多领域,同时PPM信号的调制和解调对整个通信系统的性能影响很大。

本文主要介绍了在QuartusII集成开发环境下,充分发挥数字设计的优势[1],利用Verilog HDL实现PPM系统,并通过时序仿真结果来验证设计方案。

PPM系统设计

PPM是利用脉冲的相对位置来传递信息的一种调制方式,其基本原理就是将码元信息表示在一个帧时间段内的某个时隙上,若一个码元由n比特组成,该帧时间段含M个长度为t的时隙,则2^n=M。将n比特位编码后对应成某个时隙上的脉冲来传输该码元信息,而该帧时间段内的其他时隙上则无脉冲,从而产生PPM信号。通常帧时间段还包含一个保护时间间隔Tp ,则系统的比特率为n/(M×t+Tp)。图1即为一帧16-PPM信号示意图,其中的脉冲则表示了当前码元(0111)所对应的时隙。

PPM系统的主要原理相对简单,所以可将重点放在代码编写和系统实现方面。设计过程中最重要的是各个模块之间的接口设计,竞争冒险现象的避免等。

为透彻理解PPM系统原理及其本质,简化PPM系统的设计,故在本文所设计的PPM系统中暂不考虑保护时间间隔Tp,同时取M=4,即设计一个4-PPM系统,以便于通过仿真来验证系统性能。

调制系统

通过上述原理介绍,可知PPM信号的调制实际上是一个计数输出脉冲的过程[2],对时隙信号进行计数,当它跟调制数据相等时就在相应的时隙输出高电平“1”,其他时隙均输出低电平“0”。

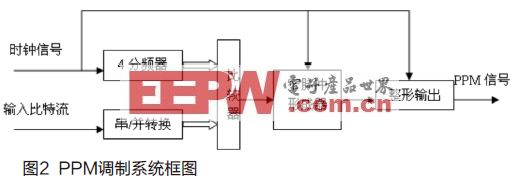

图2是PPM调制系统的框图,主要由串/并转换、4分频器、比较器、窄脉冲形成器、整形输出等5个模块。其中,串/并转换模块主要完成对输入比特流的二进制编码[3];4分频器用于生成帧时间段内的4个时隙;比较器完成对上述两模块输出的高低对应位的匹配比较;窄脉冲形成器用于对比较器的输出做成型滤波,限制PPM脉冲的带宽,从而减小该PPM脉冲对相邻频带内信号造成的干扰;整形电路仅用D触发器实现,主要功能是锁存PPM窄脉冲,与时钟同步,从而避免竞争冒险现象[3~4]。

解调系统

在设计PPM解调系统时,考虑到PPM信号的产生原理,不难发现当输入比特流为连续的“1”串或连续的“0”串时,PPM信号脉冲的间隔保持恒定,为4个时钟周期。而只有在输入比特流从“1”变为“0”或者从“0”变为“1”时,PPM信号脉冲的间隔才会发生变化[5]。所以可根据接收到的PPM信号脉冲间隔的不同来完成解调,判断原输入比特是“1”还是“0”。

根据上述解调模型,可设计PPM解调系统框图如图3所示,主要由时钟提取电路、脉冲位置检测电路、译码器、整形输出等模块构成。其中,时钟提取电路包括时隙同步[6]、帧同步和字同步[7]等,为简单起见,在本设计中省略了时钟提取模块。脉冲位置检测电路主要包括最短脉冲位置检测、最长脉冲位置检测。值得注意的是,在检测最短脉冲位置时,需要移位两个时钟周期后再和原PPM信号相与才能判别出其位置,这是因为当数据信号从“1”变为“0”的过渡阶段,表示“1”的PPM信号前沿和表示“0”的PPM信号前沿间距为2个时钟周期。同样,整形输出模块也是依靠触发器来锁存数据,完成整形。

fpga相关文章:fpga是什么

分频器相关文章:分频器原理

评论