HDLC的DSP与FPGA实现

引言

本文引用地址:http://www.amcfsurvey.com/article/112019.htmHDLC(高级数据链路控制)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件或软件编程等。

HDLC的ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。有的芯片公司还有自己的标准,对HDLC的CRC(循环冗余码校验)序列生成多项式等有不同的规定。专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO(先进先出存储器)可用。对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC再外接存储器或其他电路,ASIC的简单易用性就被抵销掉了。 HDLC的软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC应用。但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不易预测。纯软件HDLC一般只能用于个别路数的低速信号处理。

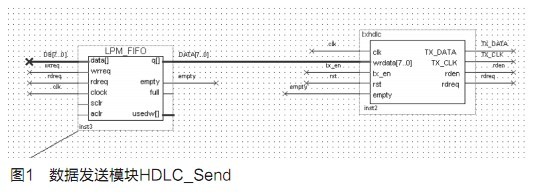

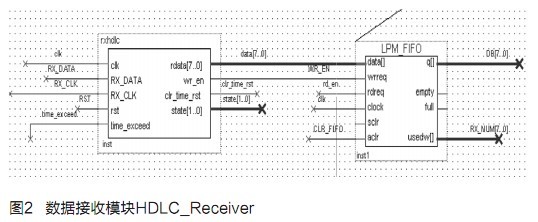

FPGA采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼顾速度和灵活性,并能并行处理多路信号,实时性能能够预测和仿真。

DSP采用软件技术处理信号,也可以反复编程使用。DSP、FPGA芯片虽成本略微高于ASIC芯片,但具有货源畅通、可多次编程使用等优点。在中小批量通信产品的设计生产中,用FPGA和DSP实现HDLC功能是一种值得采用的方法。

HDLC的帧结构和CRC校验

为了使FPGA的设计能够实现HDLC的基本功能并能按照各项标准的规定灵活采用不同的CRC校验算法,首先看一下HDLC基本的帧结构形式。

HDLC是面向比特的链路控制规程,其链路监控功能通过一定的比特组合所表示的命令和响应来实现,这些监控比特和信息比特一起以帧的形式传送。以下是ISO/IEC 3309标准规定的HDLC的基本帧结构。

其他的HDLC标准也有类似的帧结构。每帧的起始和结束以"7E"(01111110)做标志,两个"7E"之间为数据段(含地址数据、控制数据、信息数据)和帧校验序列。帧校验采用CRC算法,对除了插入的"零"以外的所有数据进行校验。为了避免将数据中的"7E"误为标志,在发送端和接收端要相应地对数据流和帧校验序列进行"插零"及"删零"操作。

评论