用PLD简化边界扫描测试

引言

本文引用地址:http://www.amcfsurvey.com/article/111150.htm随着JTAG标准IEEE1149.1的定型,及随后开始在集成电路Intel 80486中采用,边界扫描测试已被广泛应用于测试印刷电路板的连接,以及在集成电路内进行测试。边界扫描测试受到设计人员的欢迎,因为它能够在线测试,而无需昂贵的钉床在线测试设备。然而,在大的电路板上,边界扫描链路很长,电路板设计人员面临着多种挑战,诸如故障检测和隔离、测试时间、物理布线,同时还要管理偏移,电压转换和满足各种特殊需要。传统上使用ASSP来应对这些挑战,然而基于ASSP的解决方案更为昂贵,有固定的电平和一些端口,不允许任何的定制,还要手工干预。本文主要探讨如何利用可编程逻辑器件作为一个颇具吸引力的选择,以解决大的电路板上与边界扫描测试相关的挑战。

电路板设计人员面临的边界扫描挑战

在电信和网络路由设备中使用的那些大的电路板通常包含许多有边界扫描功能的器件。在这些板上实施边界扫描测试时,设计人员通常面临着以下挑战:

故障检测/隔离

测试长的扫描链路是困难的,因为在一个扫描链路上的故障可能会导致整个系统不能进行测试。此外,由于这些器件是处于菊花链之中,测试系统以链路中最慢的器件的速度运行。 这既增加了测试时间,还增加了成本。

物理布线至平衡时钟偏移

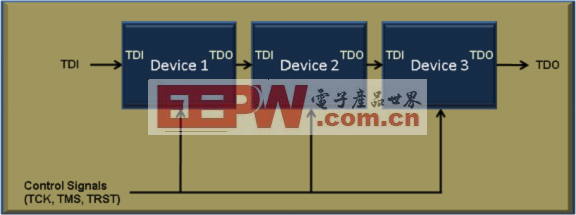

虽然扫描测试数据端口为菊花链输入,典型的控制信号,如TCK(测试时钟)TMS (测试模式设置) 和TRST(测试复位) 是直接分配的,从测试端口到扫描链路中的每一个器件。图1展示了边界扫描测试的一个典型的安排。当扫描链中器件的数量增加时可以观察到偏移的影响。解决这个问题的最常见的方法是要增加缓冲器,以便管理板上的偏移,但是这样做增加了成本和复杂性。

图1:典型的边界扫描链路

电压转换

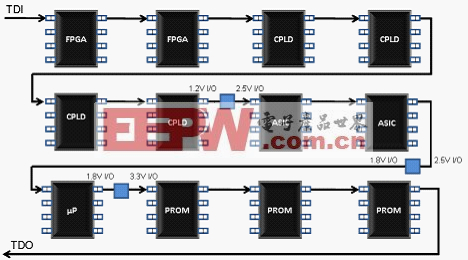

边界扫描I / O电压应该与扫描链路中连接器件之间的电压相兼容。然而,电路板上器件的I / O的信号电平往往是不兼容的。为了解决这个问题,设计人员通常添加电压转换器件。图2展示了这样一个扫描链路,其中元件具有不同的I / O电压。当一个器件的I / O电压与链路中的下一个器件的I / O电压不同时,已在扫描链路中插入一个电压转换器。在这个例子中,根据 I / O的电压,在扫描链路中的器件已放在一起。当器件的I / O电压不能放在一起时,更多的电压转换器可能需要插入到扫描链。

图2:工作在不同I / O电压的器件的扫描链路

评论