多功能数据采集处理系统实现

引言

本文引用地址:http://www.amcfsurvey.com/article/110979.htm数据采集与处理系统的设计是现代信号处理系统的基础,被广泛应用于雷达、通信、图像处理等领域。近年来,随着信息科学的高速发展,人们面临的信号处理任务越来越繁重,对实时信号数据采集处理系统的要求也越来越高。所用系统要求具有处理大量高速数据的能力,这就要求系统硬件达到很高的运算速度,并且软件处理程序也尽可能优化,以保证系统的实时性。同时,伴随着电子产品应用的多样化,电路设计的通用性也受到了大家的重视。

器件选型

A/D采样芯片

凌力尔特(Linear)的LTC2260是一种14 bit ADC,它具有105 Msps的采样率,功耗仅为106mW,显著减少了用于高速数据采集的功率预算,同时集成有高性能采样保持电路,提供CMOS兼容的输出,输入信号和采样时钟均支持差分模式。LTC2260具有以下特点:信噪比73.4dB,无杂散动态范围85dB,单1.8V电源,满功率带宽800MHz,CMOS、DDR CMOS或DDR LVDS输出,可选输入范围1VP-P 至 2VP-P。

在FPGA的选型中,通过对算法所需资源的估算和充分考虑器件的适用性,选用Altera公司StratixⅢ系列的EP3SE260。

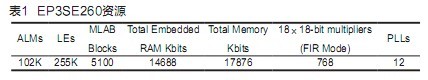

StratixⅢ拥有功能强大的DSP模块,速度高达550MHz,具有896个18×18的乘法器,支持可变位宽,支持基本乘法器、求和、累加、级联、取整、饱和以及桶形移位寄存器等功能。EP3SE260资源如表1所示。

本设计中DSP选用ADI公司的新一代ADSP TS201S数字信号处理器,兼有FPGA和ASIC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理领域。ADSP TS201S采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式系统,专为大的信号处理任务和通信结构优化。

硬件电路设计

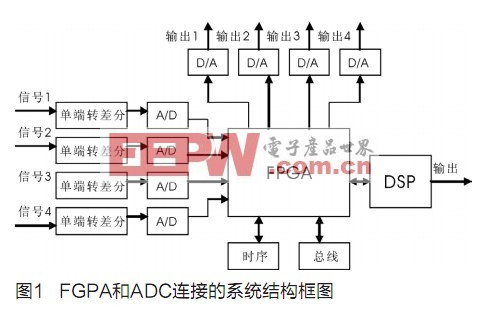

本系统中设计了四路A/D,采样后的数字信号送到FPGA进行预处理,FPGA同时为系统提供时钟、对A/D和D/A进行控制、与DSP进行数据交换,还要为CPCI接口的实现提供时序逻辑和通信接口,DSP做相应的算法处理,四路D/A可提供测试信号和自检信号,系统结构框图如图1所示。

评论