新型雷达数字电路便携式自动测试系统设计

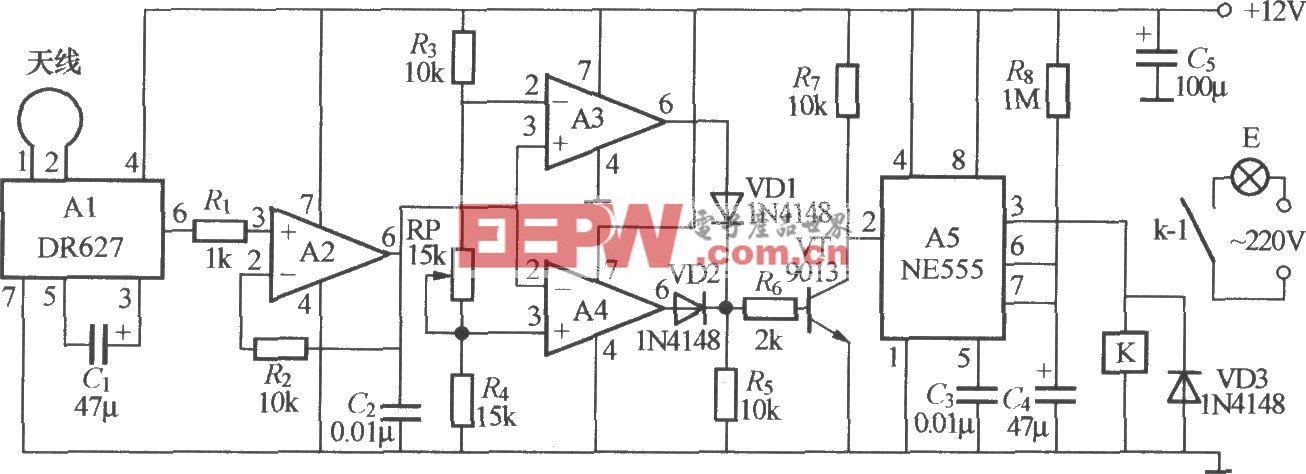

BS Interface Pod模块

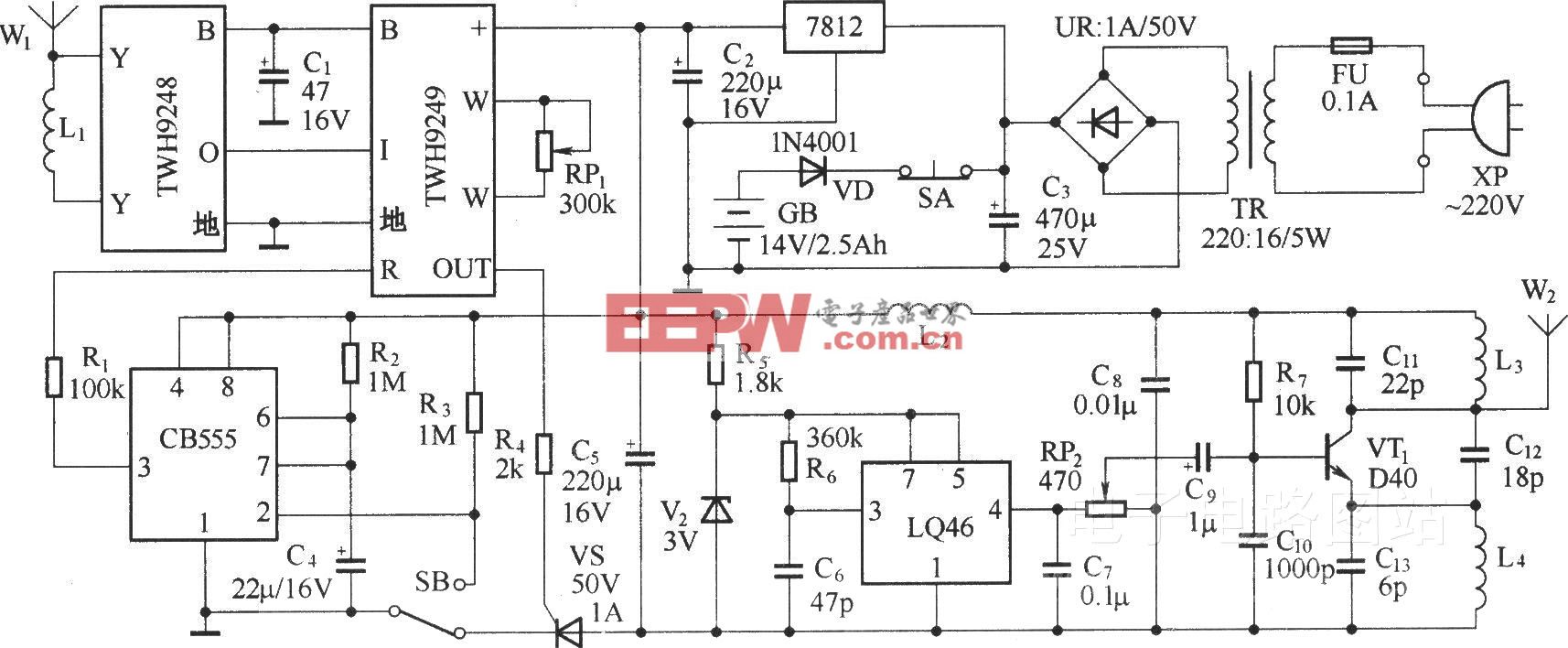

本文引用地址:http://www.amcfsurvey.com/article/109083.htmBS Interface Pod模块,作为测试输入/输出信号传输的中间级模块,主要实现JTAG-Control-PCI-USB控制器与BUT之间测试通道的扩展和信号的同步与缓存。FPGA(Altera公司,EP20K160EBC365-1)是本电路设计的核心,其功能是将前级JTAG-Control-PCI-USB控制器发出的不同的控制信号转换成UUT测试终端能够识别的TAP控制信号,保证TDI、TCK、TMS、TRST准确施加到UUT的测试端,同时将采集到的TDO信号返回给测试前端控制模块。74LVC125(Buffer)则用来完成信号暂存,输出级的74LVC125还可增强信号的扇出能力。整个BS Interface Pod模块采用抗EMI(电磁干扰)屏蔽封装,前面板预留4个20Pin的JTAG控制端口,另外设计了一个电源指示灯,用于上电确认。

测试系统软件设计

系统软件在Windows XP环境下采用Visual C++6.0及National Instruments公司的LabWindows 6.0集成开发环境完成。Visual C++ 6.0能够提供丰富的Windows程序开发功能,灵活性强、编程效率高;LabWindows 6.0提供了多种接口协议、丰富的控件及仪器驱动程序,其支持虚拟仪器技术的特性是其它开发环境无法比拟的,同时它提供了丰富的软件包接口,为软件开发提供了极大的方便。

软件设计采取了软件模块化及自顶向下的设计原则,首先根据MERGE原则划分电路模块,将测试程序分割成不同的测试模块,其次采用宏的方式构建标准的测试模块并优化模块接口,然后将其它待测模块与该模块接口进行有效链接,再分别进行编译及调试,最后一起进行合并构建完整的测试体。在开发过程中,将该软件分为若干模块不但减少了软件的工作量,而且对于函数的公共部分进行了类的封装,提高了模块的复用性,同时提高了软件本身的可测试性。

测试优化

为减少ATE在故障诊断中误判的概率,系统采用加权伪随机向量关系生成、插入间隔刷新测试矢量优化测试矢量和测试过程。

(1) 加权伪随机测试矢量生成:加权伪随机测试矢量生成能够利用较短的测试码长度(即较短的测试时间)达到较高的测试故障覆盖率。为了缩短测试码并改进故障覆盖率,这种测试矢量生成方式可以调节在输入端产生0或1的概率,有效检测到难检测的故障。在伪随机测试码中,每个输入端产生0或1的概率为50%。

(2) 插入式间隔刷新:由于数据线具有一定的电平保持特性,因此对于一组数据总线I/O而言,在BS-Cell处于读状态时(如处于Update状态),Cell单元的Output Enable Control Cell处于有效状态,测试矢量通过BS-Cell施加至I/O数据总线,如果下一个时钟节拍,BS-Cell处于写状态(如处于Capture状态),由于数据线的电平保持特性,则有可能在此时间,BS-Cell所Capture回读的数据为上一个时钟节拍的Update数据,造成测试不稳定。解决的办法是在每一次读状态结束后,系统根据读状态的间隔时间,随机产生一组与上一组测试矢量不同的数据,命名为*data,对I/O总线进行间隔刷新。

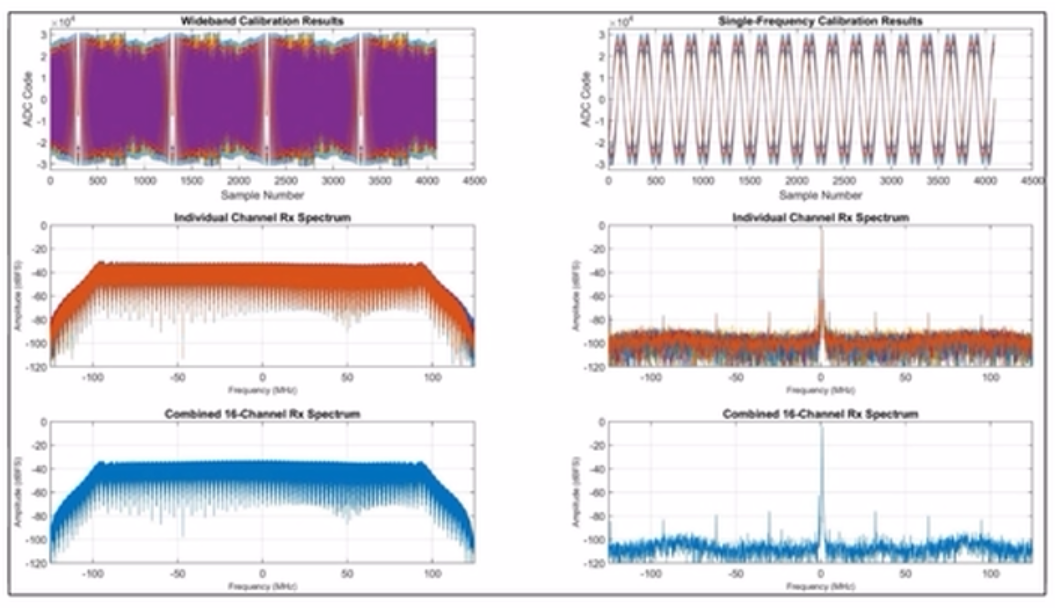

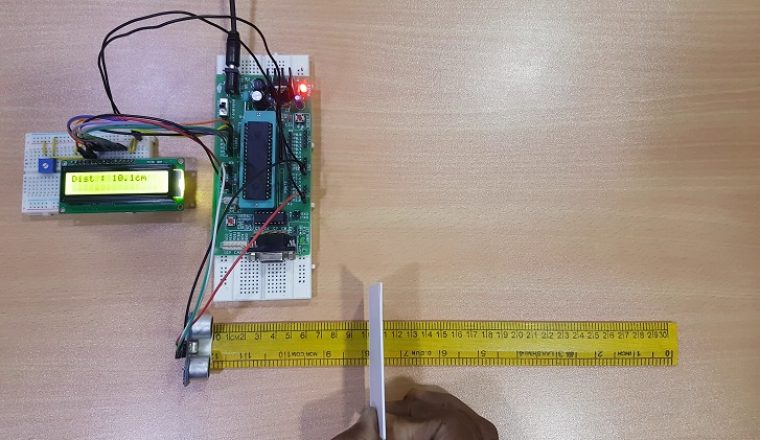

实验结果及分析

现以某新型雷达点迹处理数字电路为例进行系统功能验证。整个电路采用DSP+FPGA的设计架构,其主要芯片包括:5片DSP(ADSP21060)、2片FPGA(Atlera Flex EPF10K系列)、8片双口RAM(QFP封装),其他E2PROM、HC244(SOP封装)、HC245(SOP封装)等。电路设计复杂,芯片多,PCB布局布线密度大,采用ICT、功能测试TPS开发难度大。

利用本边界扫描自动测试系统,结合MERGE方法,对上述电路板进行TPS开发实验及故障诊断,测试结果如图4所示。

插入模拟故障(U8-6 stuck to 0),重新仿真:扫描链测试→PASS→B-Scan器件簇测试→PASS→NB-Scan器件簇测试→Failed (Report: Pin(s): U3-25,R26-2,U8-6,R26-1 possible stuck at low,the BS nodes is U31-21(R/W))。

上述仿真结果表明,融合MERGE方法所构建的基于边界扫描的板级自动测试系统,自动化程度高,故障隔离准确有效。

评论