负载点降压稳压器及其稳定性检查方法

引言

本文引用地址:http://www.amcfsurvey.com/article/108616.htm即使拥有简单易用的器件配合,但有时候仍然很难单凭计算去预计控制环路的稳定性。然而,有一个简单的方法可以在无需使用昂贵的网络分析仪下,计算出任何开关电源的0dB交叉频率及相位裕度。下面,我们将解释设立测试电路的方法,以及除了负载瞬态测试外,还有什么方法可更深入了解某设计的控制环路稳定性。

负载点稳压器的特性

一般的负载点电压调节都会把诸如是5V的低输入电压降低至2.5V、1.8V、1.1V或甚至更低的输出电压,而不少要求低输入电压的应用均倾向使用大电流。FPGA及ASIC这两种电路是设有负载点稳压器的典型电源负载的例子,它们均具有特殊的电源管理要求,尤其是高性能的FPGA,一般均要求多个电源轨,例如芯核和输入/输出需要两个电源轨是很常见的情况。可是,有些FPGA需要的电源轨数量更多,其真正的电流要求则视FPGA的实际用途而定。对于某些FPGA来说,其他需要注意的地方包括供电电压的单调启动及各电源轨的上电定序。

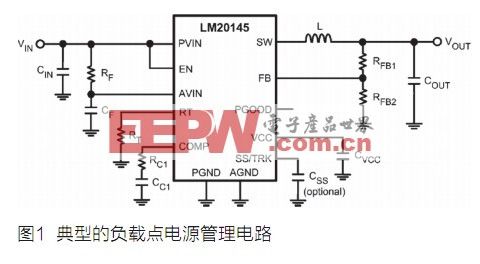

基于以上的要求,单靠一个电源管理电路实不足担当FPGA或类似负载的负载点电源。美国国家半导体的LM20000负载点稳压器系列具备各种规格,能够在设计过程中互相替换。假如FPGA的最终代码在开发期间被修改或被要求需要更大的电流时,可以改用LM20000系列中具备更大电流额定的成员,而此期间无需再花时间重新设计,因为系列中所有成员的特性均相互近似。假如一个系统采用多个不同的开关频率,便很容易产生诸如差拍现象等频率问题,而通过将多个负载点稳压器同步化便可解决这一问题。这些稳压器将会起动进入一个具备单调斜波特性的预偏置负载,以防止出现某些FPGA或ASIC的锁存或类似行为。配合软启动及追踪功能,便能够根据个别FPGA或ASIC的类型来紧密控制起动。图1所示为一个典型的大电流负载点电源的例子。由于电源管理电路内同时包含了高边及低边功率晶体管,因此只需选用少量的外置元件及进行简单的优化程序便可。

评论