ADF4108在宽带X波段频率合成器中的应用

引言

本文引用地址:http://www.amcfsurvey.com/article/107008.htm现代雷达系统对频率源的精度、分辨率、带宽、转换时间及频谱纯度等提出了越来越高的要求,性能卓越的频率源均通过锁相环频率合成技术来实现,本文所讨论的就是基于锁相环路的同步原理,由一个高准确度、高稳定度的参考晶体振荡器,综合出大量离散频率的一种技术。由于ADF4108芯片的工作带宽宽(最大带宽8GHz)、集成度高,因此只需要少量的外围电路就可以构成一个宽带、低噪声、低功耗、高稳定度的X波段频率合成器。该器件适用于高频无线系统,如宽带无线接入、卫星通信、仪器仪表、无线局域网和无线射频基站。ADF4108是较高的PLL频率合成,该器件可用来实现无线接收器和发射系统中的上变频和下变频部分的本地振荡频率。

锁相环频率合成器的基本原理

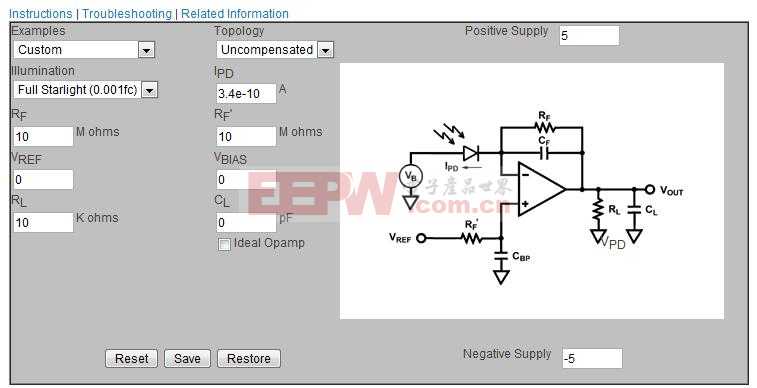

锁相环路(PLL)通常由鉴相器(PDF)、环路滤波器(LF)、压控振荡器(VCO)和可变程序分频器组成。锁相环路是一个相位误差控制系统,它比较输入信号与压控振荡器输出信号之间的相位差,产生一个对应于两个信号相位差的误差电压,该电压经处理后调整压控振荡器的频率(相位)。当环路锁定时,输入信号与压控振荡器输出信号频差为零,相位差不再随时间变化,此时误差控制电压为一固定值,压控振荡器输出频率与输入信号频率相等。锁相环路的这一特点,使它在自动频率控制中得到应用,以实现精确的频率控制。环路在锁定时要得到一定的控制电压,则鉴相器必须有一个非零的输出,即f0=fr,环路作用必须有相位差,相位差维持着两信号的同步,使输出信号频率稳定。锁相环基本原理如图1所示。

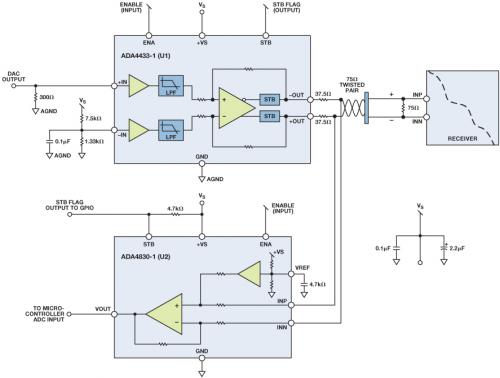

可变程序分频器(N)的作用是使压控振荡器的输出频率经分频后再与参考频率进行相位比较,从而产生误差控制电压,并以误差控制电压来调整压控振荡器的相位。锁相环路对高稳定度的参考振荡器(通常是晶体振荡器)锁定,环路串接可编程的程序分频器,通过编程改变程序分频器的分频比R、N,从而获得N/R倍参考频率的稳定输出。频率合成器输出频率f0与晶体振荡器参考频率fr的关系为:

其中,R是固定分频比,N是程序(可变)分频比,fr是晶振输出的参考频率,f0是频率合成器的输出频率。

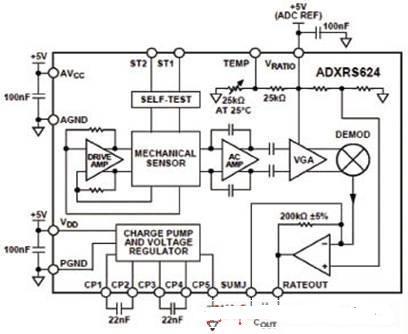

电路设计、噪声分析及仿真

ADF4108主要由一个低噪声数字鉴相器(PDF)、一个精密电荷泵、一个可编程参考分频器、可编程A(6bit)及B(13bit)分频计数器和一个双模分频器(P/P+1)构成。在这里,随模式控制高、低电平的不同,双模分频器采用两个不同的分频模数P+1和P。双模分频器的输出同时驱动两个可编程分频器,他们分别预置在A和B(A

压控振荡器输出的信号经N次分频后送入鉴相器中作为一路鉴相信号,参考晶振输出的标准信号经参考分频器R次分频后送到鉴相器中作为另一路鉴相信号。鉴相器的输出反映两路鉴相信号相位误差特性的电流序列脉冲,经电荷泵的作用输入到低通滤波器中,低通滤波器将电流转换成VCO的控制电压,同时对噪声及鉴相输出的纹波等干扰进行抑制,鉴相器内部还有一个可编程延迟单元,用来控制翻转脉冲的宽度,这个翻转脉冲保证鉴相器的传递函数没有死区,因此,降低了相位噪声和参考杂散。VCO输出与其输入端控制电压相应的工作频率。

低通滤波器相关文章:低通滤波器原理

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理 晶振相关文章:晶振原理 锁相环相关文章:锁相环原理

评论